## UNIVERSITY OF CALIFORNIA Santa Barbara

A Technology Incorporating Selective Area Regrowth for High Uniformity, Low Phase Noise, Single-Level Metal High Electron Mobility Transistors (HEMTs)

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

by

Kürşad Kızıloğlu

## Committee Members:

Professor Umesh K. Mishra, Chair Professor Nadir Dağlı Professor Stephen P. DenBaars Professor Mark J.W. Rodwell

December 1996

UMI Number: 9727719

Copyright 1996 by Kiziloglu, Kursad

All rights reserved.

UMI Microform 9727719 Copyright 1997, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103 The dissertation of Kürşad Kızıloğlu is approved

$\mathcal{M}$  . W

DerBn

The thertal

June Ming

Committee Chair

December 1996

December 26, 1996

©

Kürşad Kızıloğlu

1996

Bugünümü borçlu olduğum sevgili Anneciğime, Babacığıma ve yaşamımın son 5.5 yılını paylaştığım sevgili eşim Zarina 'ya...

To my dearest parents, Nezihi and Seniha Kızıloğlu, to whom I owe where I am today, and to my dearest wife, Zarina, for being with me for the last 5.5 years of my life...

## Acknowledgments

A task of the magnitude of this Ph.D. thesis would simply not have been achievable were it not for the efforts and helping hands of many of my friends, colleagues, support staff, and professors. My first and foremost sincere indebtedness goes to Professor Umesh Mishra, for whom I was his first student upon his arrival at UCSB, and who gave me his unwavering support throughout the six years of my Ph.D. research, both in good and bad times. I truly hope to be able to make him proud of me in my future career as a researcher and scientist. I would like to extend my special thanks to Professor Nadir Dagli, not only for being in my Ph.D. committee, but also being instrumental in my admission to UCSB and being my primary advisor in my master's studies here. I have also enjoyed the contributions and insight of Professors Stephen DenBaars and Mark Rodwell.

Throughout my long years of stay at UCSB, I have had the privilege of meeting many bright students from whom I learned a great deal. The intellectual capability of all these great minds is not something that one can find elsewhere easily. I would like to thank specially the past and present members of Professor Mishra's group: Jennifer Bishop, David Holcombe, Weinan Jiang, Nguyen Nguyen, Jeff Shealy, Willy Yin, James Champlain, Prashant Chavarkar, James Ibbetson, Dave Kapolnek, Peter Kozodoy, Lee McCarthy, Primit Parikh, Gia Parish, Rob Underwood, Ramakrishna Vetury, Jeff Yen, Yi-Feng Wu. I started my early regrowth experiments with Majid Hashemi, who helped establish the technology. Bernd Keller was instrumental in getting the regrowths to work and I enjoyed working with him a great deal. Stacia Keller helped me with some regrowth work towards the end of my dissertation. Kip Bauman offered me his help in measuring the many TLMs for ohmic contact characterization. Without the underlying material, of course, no experimental work can proceed: I owe a great deal to Prashant for finding time for me among his own Ph.D. work, and always supplying me with wafers. Mark Mondry was very helpful at those times when Prashant was overwhelmed.

I spent a great deal of time on E-Beam lithography from the day it came to UCSB. Al Patlach taught me how to use the system and I enjoyed his help, insight and humor all these years. Ernie Caine was always there to answer questions regarding E-Beam lithography and I used his suggestions a great deal. The past and present cleanroom staff were instrumental in keeping the facilities

going, and all of us that work there owe them a lot: Gerry Robinson, Don Zak, Bruce Zehnter, Brian Carralejo, Dan Cohen, Tom Reynolds and Jack Whaley. For the well-being of our everyday life at the Department and on campus, I also owe thanks to the Word Processing Staff Robin Jenneve, Claudia Leufkens, Heather Simioni, Scott Smith, Graduate Student Office Staff Margie Clark, Linda James, Melany Miners, Roci Rojas, Budget Office Staff Jan Holtzclaw, Sharon Murray, Diane Onley, Electronics Shop Staff Dale Clark, Jerry Jones, Avery Juan, Bob Stevenson, Computer Support Staff Dean Carter, Terry Light, Jacques Girod, the past and present Solid State Office Assistants Kathy Kramer, Janie Lee, and the International Students Office Staff, Vince Aihara, Martha Gomez, Ambi Harsha, and Tanya Plant.

I am also indebted to my friends for providing me with the emotional support, whenever I needed it: Ersan Demiralp, Dan Hamilton, Koral Ilgün, Erdal Paksoy, Serdar and Veronica Sarıçiftçi.

The last but not the least, I owe where I am today to my parents, who spared no sacrifice in bringing me up, and who still support me in all the steps I take and the decisions I make. Perhaps one of my best gains out of my experience at UCSB was finding my wife, Zarina, whose selfless help and support has always been there for me.

#### Vita

November 7, 1966: Born, Ankara, Türkiye

July 1988: B.S., Electrical and Electronics Engineering, Middle

East Technical University, Ankara, Türkiye

Sept. 1988 - Aug. 1990: Research Assistant, Department of Electrical and

Computer Engineering, University of California, Santa

Barbara

August 1990: M.S., Electrical and Computer Engineering, University

of California, Santa Barbara

Sept. 1990 - Sept. 1996: Graduate Student Researcher, Department of Electrical

and Computer Engineering, University of California,

Santa Barbara

Oct. 1996 - Dec. 1996: Member of Research Staff, Hughes Research

Laboratories, Malibu, CA

December 1996: Ph.D., Electrical and Computer Engineering, University

of California, Santa Barbara

#### **Publications**

#### Master's Thesis:

"Modelling and measurement of wave effects in high-speed GaAs digital circuit interconnects", Department of Electrical and Computer Engineering, University of California, Santa Barbara, 1990

## Conference Abstracts and Journal Publications:

- 1. K. Kiziloglu, B.P. Keller, P.M. Chavarkar, X. Cao, S.P. DenBaars, U.K. Mishra, "Selective area growth as an enabling technology for high-uniformity single-level metal HEMTs," presented at the 38th Electronic Materials Conference held in Santa Barbara, CA, June 26-28, 1996.

- 2. P. Parikh, W. Jiang, P.M. Chavarkar, K. Kiziloglu, B. Keller, S.P. DenBaars, U.K. Mishra, "A new FET-based circuit technology: the SASSFET," IEEE Electron Device Letters, July 1996, vol. 17, pp. 375-377.

- 3. P. Parikh, K. Kiziloglu, M. Mondry, P. Chavarkar, B. Keller, S. DenBaars, U. Mishra, "InP-based devices and their applications for merged FET-HBT technologies," Microwave and Optical Technology Letters, February 20, 1996, vol. 11, pp. 121-125.

- 4. K. Kiziloglu, B.P. Keller, P.M. Chavarkar, S.P. DenBaars, U.K. Mishra, "Selectively regrown ohmic contacts for high frequency and low noise FETs," in Proceedings of IEEE/Cornell Conference on Advanced Concepts in High Speed Semiconductor Devices and Circuits, August 7-9, 1995, Cornell University, Ithaca, New York, pp. 303-312.

- 5. K. Kiziloglu, M.M. Hashemi, S.P. DenBaars, U.K. Mishra, "On the interface resistance of regrown GaInAs on InP," Solid-State Electronics, April 1995, vol. 38, pp. 905-908.

- P. Parikh, K. Kiziloglu, M. Mondry, P. Chavarkar, B. Keller, S. DenBaars, U. Mishra, "An n-HJFET - pnp HBT process for complementary circuit applications," in Proceedings of the 21st International Symposium on Compound Semiconductors held in San Diego, CA, September 18-22, 1994, ed. H. Goronkin and U. Mishra, Philadelphia: Institute of Physics Pub., 1995, pp. 663-666.

- 7. J.B. Shealy, M.M. Hashemi, K. Kiziloglu, S.P. DenBaars, U.K. Mishra, T.K. Liu, J.J. Brown, M. Lui, "High-breakdown-voltage AllnAs/GaInAs junction-modulated HEMT's (JHEMT's) with regrown ohmic contacts by MOCVD," IEEE Electron Device Letters, Dec. 1993, vol. 14, pp. 545-547.

- 8. M.M. Hashemi, K. Kiziloglu, J.B. Shealy, S.P. DenBaars, U.K. Mishra, "Ga<sub>0.51</sub>In<sub>0.49</sub>P channel MESFET," Electronics Letters, 25 Nov. 1993, vol. 29, pp. 2154-2155.

- 9. J.B. Shealy, M.M. Hashemi, K. Kiziloglu, S.P. DenBaars, U.K. Mishra, T.K. Liu, J.J. Brown, M.M. Liu, "High frequency, high breakdown AlInAs/GalnAs junction modulated HEMT's (JHEMT's) with regrown ohmic contacts by MOCVD," (in Proceedings of the IEEE 51st Annual Device Research Conference, Santa Barbara, CA, June 21-23 1993), IEEE Transactions on Electron Devices, Nov. 1993, vol. 40, p. 2115.

- L.-W. Yin, N.X. Nguyen, K. Kiziloglu, J.P. Ibbetson, A.C. Gossard, U.K. Mishra, "Device performance of submicrometre MESFETs with LTG passivation," Electronics Letters, 19 Aug. 1993, vol. 29, pp. 1550-1551.

- 11. N. Nguyen, K. Kiziloglu, J. Ibbetson, L.-W. Yin, M. Hashemi, U. Mishra, "The output conductance in GaAs air-gap MESFETs," (in Proceedings of the 50th Annual Device Research Conference, Cambridge, MA, June 22-24 1992), IEEE Transactions on Electron Devices, Nov. 1992, vol. 39, p. 2648.

- 12. M.M. Hashemi, Y. Li, K. Kiziloglu, M. Wassermeier, P.M. Petroff, U.K. Mishra, "Direct-current and radio-frequency characterization of submicron striped-channel field effect transistor structures using focused ion beam and electron-beam lithography," (36th International Symposium on Electron, Ion and Photon Beams (EIPB '92), Orlando, FL. May 26-29, 1992), Journal of Vacuum Science & Technology B (Microelectronics Processing and Phenomena), Nov.-Dec. 1992, vol. 10, pp. 2945-2948.

- 13. K. Kiziloglu, M.M. Hashemi, L.-W. Yin, Y.J. Li, P.M. Petroff, U.K. Mishra, A.S. Brown, "Rapid thermal annealing characteristics of bulk AlInAs/InP and AlInAs/GalnAs/InP high electron mobility transistor structures with planar silicon doping," Journal of Applied Physics, 15 Oct. 1992, vol. 72, pp. 3798-3802.

- 14. K. Kiziloglu, N. Dagli, G.L. Matthaei, S.I. Long, "Experimental analysis of transmission line parameters in high-speed GaAs digital circuit interconnects," IEEE Transactions on Microwave Theory and Techniques, Aug. 1991, vol. 39, pp. 1361-1367.

- K. Kiziloglu, N. Dagli, G.L. Matthaei, S.I. Long, "Experimental determination of high-speed GaAs digital circuit interconnect parameters," in 1991 IEEE MTT-S International Microwave Symposium Digest, Boston, MA, June 10-14, 1991, New York, NY, IEEE: 1991, vol. 2, pp. 639-642.

- J.A. Bishop, M.M. Hashemi, K. Kiziloglu, L. Larson, N. Dagli, U. Mishra, "Monolithic coaxial transmission lines for mm-wave ICs," in Proceedings of the IEEE/Cornell Conference on Advanced Concepts in High Speed Semiconductor Devices and Circuits, Ithaca, NY, Aug. 5-7, 1991, New York, NY, IEEE, 1991, p. 252-260.

17. G.L. Matthaei, K. Kiziloglu, N. Dagli, S.I. Long, "The nature of the charges, currents, and fields in and about conductors having cross-sectional dimensions of the order of a skin depth," IEEE Transactions on Microwave Theory and Techniques, Aug. 1990, vol. 38, pp. 1031-1036.

## Fields of Study

Studies in electromagnetics and microwave modeling Professors Nadir Dağlı and George L. Matthaei

Studies in compound semiconductor devices, fabrication and modeling Professor Umesh K. Mishra

#### **Abstract**

A Technology Incorporating Selective Area Regrowth for High Uniformity, Low Phase Noise, Single-Level Metal High Electron Mobility Transistors (HEMTs)

by

#### Kürşad Kızıloğlu

A reproducible, uniform, and reliable FET technology for various high frequency and low noise applications including receivers, transmitters, microwave and opto-electronic integrated circuits is crucial. The rapid developments in materials technologies have made it possible to investigate the fabrication of FETs, where processing and growth are continuously interleaved throughout the fabrication of devices. In this work, we report on the fabrication of a HEMT, where selective growth is employed twice to arrive at the final device: once to achieve low resistance ohmic contacts, and second time to achieve a stable epitaxial surface passivation.

We first develop a technology for non-alloyed ohmic contacts with highly doped regrowth of GalnAs on various GalnAs channel devices including AllnAs/GalnAs/InP HEMTs. For the regrowths done on HEMTs with Si doping in the AllnAs donor layer, we find that, if the doping concentration in the regrown GalnAs is low (n =  $1.5 \cdot 10^{18}$  cm<sup>-3</sup>), and HF solutions are employed in the processing steps, there exist instabilities in the contacts at higher temperatures. This is attributed to the passivation of Si dopant atoms in AllnAs by fluorine. However, we achieve temperature stable ohmic contacts with a contact resistance of 0.1  $\Omega$ ·mm regardless of the samples' exposure to HF when higher doping (n =  $7 \cdot 10^{18}$  cm<sup>-3</sup>) is incorporated in the regrowth process.

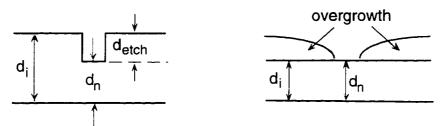

Based on the regrowth technology with which we have achieved non-alloyed, low resistance highly doped source and drain contacts, we demonstrate the feasibility of HEMTs with epitaxial surface passivation. We examine the merits and drawbacks of epitaxially passivating our devices by overgrowing both InP by MOCVD, and AllnAs by MOCVD and MBE. The implementation of epitaxial overgrowth coupled with the regrown contacts enable the following: (i) fabrication of devices with a single level of metalization for all the source, drain, and gate contacts. (ii) elimination of recess etching as lower access region

resistance is guaranteed by the overgrowth in the access regions, and (iii) devices with suppressed low-frequency and phase noise characteristics. We report on the dc, microwave, low-frequency and phase noise characteristics of these epitaxially passivated HEMTs with regrown contacts, and compare their performance to existing data in the literature.

## xiii

## **Table of Contents**

| Introduction                                                          |    |

|-----------------------------------------------------------------------|----|

| Chapter 1. Ohmic Contacts and Contact Resistance of Regrown GaInAs on | 1  |

| InP  1.1. Definitions, Models and Measurement Methods                 |    |

| 1.2. A Two-Layer TLM Method                                           |    |

| 1.3. Physics of Ohmic Contacts                                        |    |

| 1.4. Implementation of Regrown Contacts: Regrowth of GaInAs on        |    |

| InP                                                                   |    |

| 1.4.1. Measurements of Contact Resistance                             | 14 |

| 1.4.2. Experimental and Theoretical Calculation of the Interface      |    |

| Resistance                                                            |    |

| 1.5. Summary                                                          |    |

| References                                                            |    |

| Chapter 2. Effects of Rapid Thermal Annealing on Bulk AlInAs/InP and  |    |

| AllnAs/GalnAs/InP HEMT Structures with Planar Si Doping               |    |

| 2.1. Experiments                                                      |    |

| 2.2. Results and Discussions                                          |    |

| 2.2.1. 700°C and 800°C Anneals                                        | 23 |

| 2.2.1.1. Discussions on the Mobility                                  |    |

| 2.2.1.2. Discussions on the Carrier Concentration                     |    |

| 2.2.2. 900°C Anneals                                                  |    |

| 2.3. Summary                                                          |    |

| References                                                            |    |

| Chapter 3. Regrowth of n GalnAs on GalnAs Channel Devices             |    |

| 3.1. Fabrication of the TLM Patterns                                  |    |

| 3.2. Initial Regrowth Studies on FET and HEMT Structures              |    |

| 3.3. Effects of Fluorine on the Regrown Contacts                      |    |

| 3.4. Summary                                                          |    |

| References                                                            |    |

| Chapter 4. Fabrication of the HEMT                                    |    |

| 4.1. Device Proposal and Design                                       |    |

| 4.2. Initial Process Idea                                             |    |

| 4.3. Improved Process Idea                                            |    |

| 4.4. Overgrowth of AlInAs by MOCVD                                    |    |

| 4.4.1. Dummy Oxide Gate Issues                                        |    |

| 4.4.2. Completion of the Process and Results                          | 55 |

## xiv

| 4.5. Overgrowth of InP by MOCVD                                 | 57  |

|-----------------------------------------------------------------|-----|

| 4.5.1. Design and Process                                       |     |

| 4.5.2. Device Results (Dc and microwave)                        |     |

| 4.6. Overgrowth of AllnAs by MBE                                |     |

| 4.7. Phase Noise and Low Frequency (Baseband) Noise Performance | 64  |

| 4.7.1. Measurements on Devices with MOCVD InP Passivation.      |     |

| 4.7.2. Measurements on Devices with MBE AlInAs Passivation.     | 73  |

| 4.8. Summary                                                    | 73  |

| References                                                      |     |

| Summary and Suggestions for Future Work                         | 81  |

| Appendix 1. Process Notes                                       | 83  |

| Appendix 2. Electron-Beam Lithography at UCSB                   | 89  |

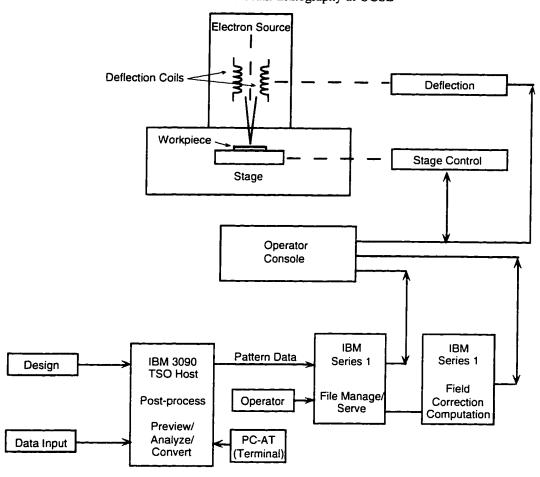

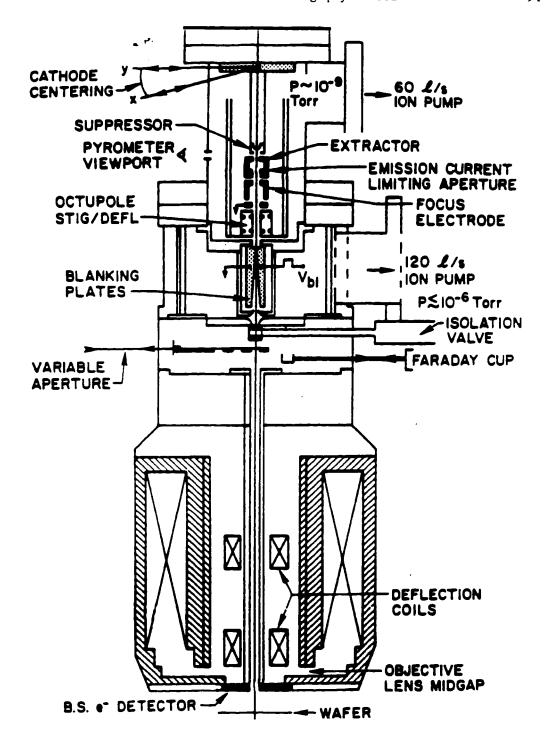

| A.2.1. E-Beam System                                            |     |

| A.2.2. E-Beam Pattern Preparation and Exposure Parameters       |     |

| A.2.3. E-Beam Lithography Process                               |     |

| A.2.4. Comments About SiO <sub>2</sub> Evaporation and Liftoff  | 94  |

| A.2.5. Effects of Atmospheric Pressure Regrowth on E-Beam       |     |

| Registration                                                    |     |

| References                                                      | 99  |

| Appendix 3. Material Safety Data Sheets                         | 101 |

| A.3.1. MSDS for PMMA                                            | 101 |

| A.3.2. MSDS for the Copolymer (PMMA/MAA)                        |     |

## Introduction

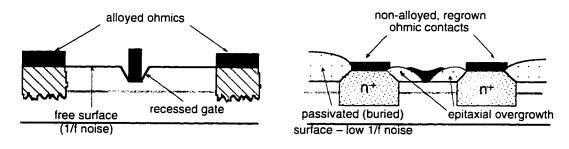

A reproducible, uniform, and reliable FET technology for various high frequency and low noise applications including receivers, transmitters, opto-electronic integrated circuits (OEICs) and microwave monolithic integrated circuits (MMICs) is crucial. In this dissertation, we report on the realization of InP based FETs that utilize developments in materials technologies, whereby processing and growth are continuously interleaved throughout the fabrication of the devices. The final devices employ selective regrowth twice: once to achieve low resistance ohmic contacts, and second time to achieve a stable epitaxial surface passivation. The implementation of epitaxial overgrowth coupled with the regrown contacts enable: (i) fabrication of devices with a single level of metalization for all the source, drain, and gate contacts, (ii) elimination of recess etching, and (iii) devices with suppressed low-frequency and phase noise characteristics.

It is recognized that ohmic contacts play an important role in the high frequency and low noise transistors as the need to reduce device parasitics and further improve device characteristics becomes more pressing. Among the various methods for establishing ohmic contacts to semiconductor devices are:

- (i) standard ohmic contacts achieved by deposition of metal on the semiconductor and subsequent alloying.

- (ii) ion implantation of dopant species (such as Si for n-type ohmic contacts) in the source and drain regions. This step is followed by a high temperature annealing process to activate the implanted dopants. Finally as is done in (i), metal is deposited and alloyed to create the ohmic contact.

- (iii)non-alloyed contacts to highly doped regrown regions in the source and drain areas.

We thus start in Chapter 1 by giving a background on the methods used to characterize ohmic contacts. We briefly talk about the physics of metal-semiconductor junctions and introduce a circuit theory based formulation methodology to tackle contacts in which current conduction takes place in two layers instead of a single one. We then use this methodology and a theoretical approach based on the physics of ohmic contacts to analyze an implementation of regrown contacts achieved with GaInAs regrowth on InP channel devices.

As mentioned above, one possible means of achieving ohmic contacts is the implantation of donor species into areas where contacts are desired. However, because implantation requires high temperature anneal steps for dopant activation, in Chapter 2 we characterize the effects of high temperature treatment on AlInAs/GaInAs/InP HEMT structures. We perform a series of annealing experiments and investigate the effects of these high temperature anneals on the mobility and the sheet carrier concentration of the electrons. We conclude the chapter by discussing the viability of implanted contacts for various applications.

In the rest of the dissertation, we concentrate our efforts in investigating highly doped regrown GaInAs contacts on InP based FETs. Regrown contacts have inherent advantages over other contact schemes in that (i) they enable non-alloyed contacts, which improves device stability and reliability, (ii) single level metal fabrication of FETs is possible, where the gate, source and drain metalizations are carried out at the same time, and perhaps most importantly, (iii) they create an enabling technology, which makes it possible to achieve good ohmic contacts to semiconductor devices regardless of the channel material. In Chapter 3, we thus investigate "homojunction regrowth" where highly doped GaInAs is regrown on GaInAs channel devices. We report on the instabilities encountered in the contacts for lower doping concentrations used in the regrown GaInAs when HF is employed in the processing steps. However, we present low resistance and temperature stable ohmic contacts regardless of the sample's exposure to HF when higher doping is incorporated in the regrowth process.

Based on the regrowth technology for achieving non-alloyed, low resistance highly n<sup>+</sup> doped source and drain contacts, we then demonstrate in Chapter 4, the feasibility of HEMTs with epitaxial surface passivation. We give fabrication details and show dc, microwave, low-frequency noise and phase noise measurement results on HEMTs with regrown contacts that have a single level of metalization for all the source, drain and gate terminals, and because of surface epitaxial passivation, that require no recess etching. We conclude the chapter by comparing our devices with the state-of-the-art.

Three appendices follow an overall summary and notes on possible directions for future work. Appendix 1 gives general processing details and is followed by Appendix 2 on electron beam lithography at UCSB. Appendix 3 lists the manufacturer's safety data sheets on the particular E-beam resists used.

## Chapter 1

## Ohmic Contacts and Contact Resistance of Regrown GaInAs on InP

Ohmic contacts are the terminals through which the semiconductor devices communicate with the outside world electrically. Good ohmic contacts should be stable with respect to both time and temperature, and should have low resistance associated with them to make it possible to access the intrinsic devices without losing much of the original information that is sent or received from the device. They continue to play an important role in today's high frequency and low noise transistors as well, as the need to reduce device parasitics and further improve device characteristics becomes more pressing. There are various methods for establishing ohmic contacts to semiconductor devices:

- (i) standard ohmic contacts achieved by deposition of metal on the semiconductor and subsequent alloying.

- (ii) ion implantation of dopant species (such as Si for n-type ohmic contacts) in the source and drain regions. This step is followed by a high temperature annealing process to activate the implanted dopants. Finally as is done in (i), metal is deposited and alloyed to create the ohmic contact.

- (iii)non-alloyed contacts to highly doped epitaxially regrown regions in the source and drain areas.

In this chapter we give a background on the methods that are used to characterize ohmic contacts and report contacts achieved by regrowth of n<sup>+</sup>-GaInAs on n-InP channel devices.

## 1.1. Definitions, Models and Measurement Methods

Figure 1.1 shows a schematic of ohmic contacts on a lateral device. The total resistance R between the two terminals is given by

$$R = 2 R_C + R_S \frac{L}{w}, {1.1}$$

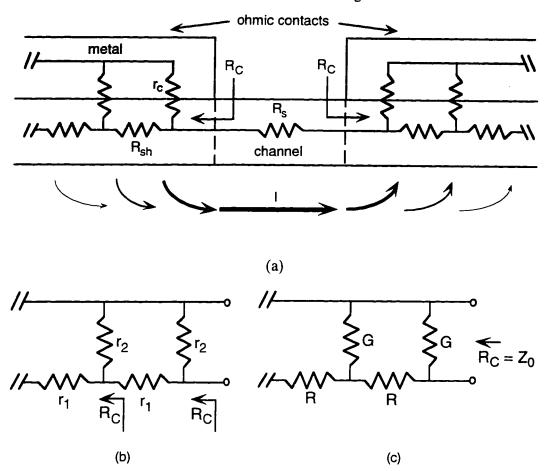

Figure 1.1.(a) Schematic cross section of a conductive channel with ohmic contacts at the ends. The current decreases exponentially as it moves away from the edges of the metalization. (b) Resistor network model for the contact resistance. (c) Transmission line model for the contact resistance.

where  $R_C(\Omega)$  is the contact resistance of the ohmic contact,  $R_S(\Omega/\text{sq})$  is the sheet resistance of the channel material, L is the separation, and w is the width of the contacts. The parameter shown in the figure as  $r_c(\Omega \cdot \text{cm}^2)$  is the specific contact resistivity and is the basic parameter that characterizes the contact between the metal and the semiconductor. It is possible to model the current conduction underneath the contacts with a resistor network as shown in Figure 1.1 (b). The current drops exponentially as it moves further into the contacts. A relevant parameter is the transfer length,  $L_t$ , under the contact, where the current has dropped to 1/e of its initial value at the edge. For modern microwave devices this value is about a micron or less. Since the dimensions of the pads provided for ohmic contacts on device mask layouts are on the order of tens of microns, the

resistor network can be assumed to be a semi-infinite one for all practical purposes <sup>1</sup>.

We can calculate the relationships among the various resistance parameters by the models shown in Figure 1.1. In Figure 1.1 (b), the resistors  $r_1$  and  $r_2$  are given in terms of the device parameters as

$$r_l = \frac{R_{sh}}{w} dx \text{ and } r_2 = \frac{r_c}{w dx}.$$

(1.2)

Utilizing the fact that we have a semi-infinite network, we can write

$$(r_1 + R_C) // r_2 = R_C,$$

(1.3)

and obtain

$$R_C^2 + r_1 R_C - r_1 r_2 = 0. ag{1.4}$$

If we now insert the values for  $r_1$  and  $r_2$  from (1.2) into (1.4), let dx go to zero, and solve for  $R_C$ , we get

$$R_C = \frac{\sqrt{r_c R_{sh}}}{w}$$

, or  $r_c = \frac{(R_C w)^2}{R_{sh}}$ . (1.5)

We can arrive at the same result from a transmission line point of view as well [3]. In this case, the resistance per unit length, R, and the conductance per unit length, G as shown in Figure 1.1 (c) are given by

$$R = R_{sh} / w \text{ and } G = w / r_c.$$

(1.6)

The well known transmission line equations for the characteristic impedance  $Z_0$  and the propagation constant  $\gamma$  are

<sup>&</sup>lt;sup>1</sup> The succeding analysis is modified slightly for cases where the contacts have finite lengths [1, 2].

1. Ohmic Contacts and Contact Resistance of Regrown GaInAs on InP

$$Z_0 = \sqrt{\frac{R + j\omega L}{G + j\omega C}} \text{ and } \gamma = \sqrt{(R + j\omega L)(G + j\omega C)}, \qquad (1.7)$$

where L and C are the inductance and the capacitance per unit length. In our case, since we have a purely resistive "transmission line", L = C = 0. Substituting the values of R and G from (1.6) into (1.7), and remembering that the input impedance of an infinite transmission line is its characteristic impedance, we obtain

$$Z_0 = R_C = \frac{\sqrt{r_c R_{sh}}}{w} \text{ and } \gamma = \frac{1}{L_t} = \sqrt{\frac{R_{sh}}{r_c}},$$

(1.8)

which is the same result as obtained in (1.5).

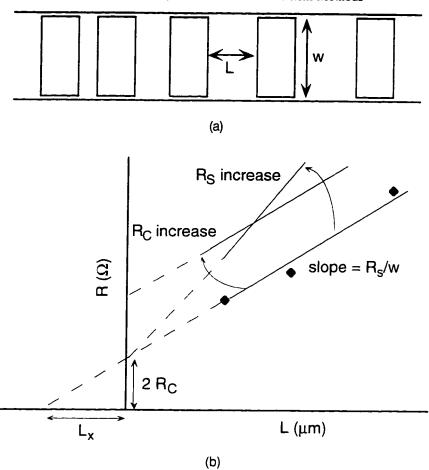

To measure the contact and sheet resistances experimentally, a test pattern comprising of ohmic contacts with varying separations on isolated bars is used as shown in Figure 1.2 (a). To obtain the contact and sheet resistances of the structure, the measured resistance values are plotted with respect to the contact separation as shown in Figure 1.2 (b). From a linear fit,  $R_C$  and  $R_S$  can be quickly extracted as shown. The x-intercept  $L_x$ , is related to the transfer length,  $L_t$ . From (1.1),  $L_x$  can be written as

$$L_x = \frac{2R_C w}{R_S}. ag{1.9}$$

By substituting  $R_C$  in terms of  $r_c$ , and  $r_c$  in terms of  $L_t$  from (1.8), we obtain

$$L_x = \frac{2 R_{sh}}{R_S} L_t. {(1.10)}$$

Normally the sheet resistance under the contact,  $R_{sh}$ , and the sheet resistance of the channel,  $R_S$  are different from each other as the contact is formed by alloying, implantation of dopants, or regrowth of highly doped material. Therefore additional measurements would be required if the values of  $r_c$ ,  $R_{sh}$ , or  $L_t$  were desired. However, for practical considerations,  $R_{sh} = R_S$  is generally assumed [2].

Figure 1.2.(a) Pattern used for contact and sheet resistance measurements. (b) The fitted line graphs from which the  $R_{\rm C}$  and  $R_{\rm S}$  can be extracted.

Figure 1.2 (b) also shows graphically that an increased slope in the fitted line will point out to an effective increase in the sheet resistance of the channel, and a parallel upward shift will be interpreted as an increase in the ohmic contact resistance.

### 1.2. A Two-Layer TLM Method

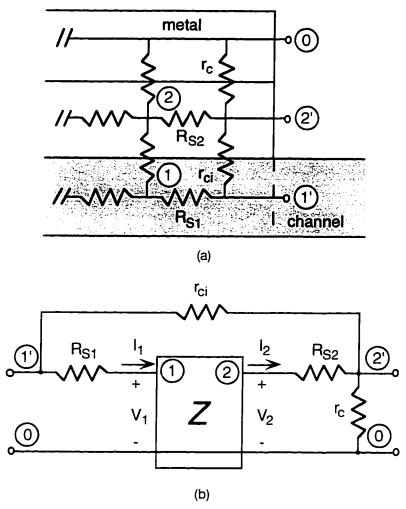

We now present a method that we have developed for analyzing a contact resistance scheme, where current conduction takes place in two layers under the contact as shown in Figure 1.3 (a). This contact scheme is encountered, for example, when a highly doped low bandgap material is regrown on a conductive channel or an ohmic contact region of higher doping is achieved on the original

conductive channel either by metalization and alloying or dopant implantation and activation. The contact resistance  $R_C$  of the semi-infinite resistor network is, by definition, the input resistance of the 2-port between the nodes 1 and 0. We note that the two-ports defined by the nodes 1, 2, 0, and the nodes 1', 2', 0 are identical. Representing the networks in terms of their impedance parameters, we can write

$$[Z] = [Z'].$$

(1.11)

The impedance parameters relate the currents flowing into the network to the voltages at the terminals and are given by

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} Z \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}, \text{ where } \begin{bmatrix} Z \end{bmatrix} = \begin{bmatrix} z_{11} & z_{12} \\ z_{21} & z_{22} \end{bmatrix}. \tag{1.12}$$

Figure 1.3 (b) depicts the circuit diagram of the network with the semiinfinite ladder replaced by its equivalent two-port representation. We note that the resistors  $R_{SI}$ ,  $R_{S2}$ , and  $r_c$  are in cascade connection with the original network, which naturally leads to representation in ABCD parameters. With the current and voltage directions as shown in Figure 1.3 (b), the ABCD parameters of a twoport network are defined as

$$\begin{bmatrix} V_1 \\ I_1 \end{bmatrix} = \begin{bmatrix} A & B \\ C & D \end{bmatrix} \begin{bmatrix} V_2 \\ I_2 \end{bmatrix},$$

(1.13)

and they are related to the Z parameters through [4]

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} \frac{z_{11}}{z_{21}} & \frac{z_{11}z_{22} - z_{12}z_{21}}{z_{21}} \\ \frac{1}{z_{21}} & \frac{z_{22}}{z_{21}} \end{bmatrix}.$$

(1.14)

The ABCD matrices for a series and a parallel resistor R are easily computed to be  $\begin{bmatrix} 1 & R \\ 0 & 1 \end{bmatrix}$  and  $\begin{bmatrix} 1 & 0 \\ \frac{1}{R} & 1 \end{bmatrix}$  respectively. The ABCD parameters of the final network

before the parallel  $r_{ci}$  connection is thus given by the matrix product

Figure 1.3.(a) A 2-port resistor network model for analyzing a two-layer conduction scheme under the ohmic contact. (b) Equivalent circuit diagram for the resistor network

$$\begin{bmatrix} A^* & B^* \\ C^* & D^* \end{bmatrix} = \begin{bmatrix} 1 & R_{S1} \\ 0 & 1 \end{bmatrix} \begin{bmatrix} A & B \\ C & D \end{bmatrix} \begin{bmatrix} 1 & R_{S2} \\ 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 \\ \frac{1}{r_c} & 1 \end{bmatrix}.$$

(1.15)

The easiest way to connect the resistor  $r_{ci}$  in parallel is by utilizing Y parameter representation, which relates the currents at the network terminals to the voltages. Thus, we first convert the  $A^*B^*C^*D^*$  matrix to its equivalent Y parameter representation, [Y] [4], and then compute the Y parameters of the final two port as

$$[Y'] = [Y^*] + \frac{1}{r_{ci}} \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix}, \tag{1.16}$$

where the second term is the Y parameter matrix for the resistor,  $r_{ci}$ . We end the matrix manipulation by converting the matrix Y' to Z', its equivalent Z parameter representation. The equality (1.11) represents four coupled nonlinear equations in eight variables. Given any four variables, the remaining four unknowns can be solved numerically. For example, if  $R_{SI}$ ,  $R_{S2}$ ,  $r_c$ , and  $R_C$  (=  $z_{II}$ ) are given, we can solve for  $r_{ci}$ ,  $z_{I2}$ ,  $z_{2I}$ , and  $z_{22}$ . Clearly, the resistances have to be entered into the equations for a small incremental length, dx. Thus, instead of the symbolic representation in Figure 1.3 (b), the resistances are entered as

$$r_{ci} \leftarrow \frac{r_{ci}}{dx \, w}, \, r_c \leftarrow \frac{r_c}{dx \, w}, \, R_{S2} \leftarrow R_{S2} \frac{dx}{w}, \, \text{and} \, R_{S1} \leftarrow R_{S1} \frac{dx}{w}.$$

(1.17)

## 1.3. Physics of Ohmic Contacts

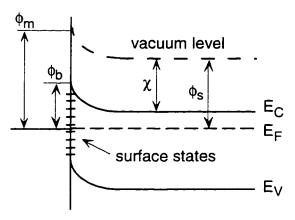

A metal-semiconductor contact is considered ohmic if it can support the required current across the interface without appreciable voltage drop [5]. In compound semiconductors, the metal-semiconductor Schottky barrier height is typically determined by Fermi-level pinning as shown in Figure 1.4.

The electron transport across the metal-semiconductor interface occurs in two main regimes: thermionic and field emission [6, 7]. The particular regime of

Figure 1.4. Schematic band diagram of a metal-semiconductor junction.  $\phi_m$  and  $\phi_s$  are the metal and the semiconductor workfunctions,  $\chi$  is the electron affinity of the semiconductor, and  $\phi_b$  is the Schottky barrier height.

operation depends on the relative magnitudes of the thermal energy of the electrons, kT, where k is Boltzman's constant and T is the temperature, and a characteristic tunneling energy  $E_{00}$  defined by

$$E_{00} = \frac{q\hbar}{2} \sqrt{\frac{N_D}{m^* \varepsilon}},\tag{1.18}$$

where q is the electronic charge,  $\hbar$  is Planck's constant divided by  $2\pi$ ,  $N_D$  is the concentration of donors,  $m^*$  is the effective mass of the tunneling electrons, and  $\varepsilon$  is the dielectric constant of the semiconductor. The electrons can traverse the potential barrier if they have sufficiently high thermal energy or they can tunnel through it if it is sufficiently thin. In an intermediate case, the electrons have enough thermal energy to reach the thinner part of the barrier, and then tunnel there. It is the tunneling action that enables ohmic contacts from metal-semiconductor junctions. Qualitatively, the three regimes are described as follows:

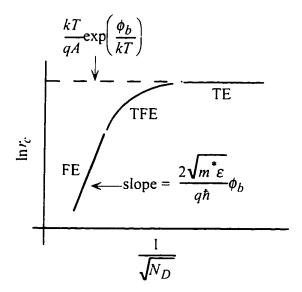

$$\frac{kT}{E_{00}} >> 1$$

thermionic emission

$$\frac{kT}{E_{00}} \approx 1$$

thermionic-field emission

$$\frac{kT}{E_{00}} << 1$$

field emission (tunneling) (1.19)

The specific contact resistivity associated with a junction is given by

$$r_c = \frac{1}{\frac{\partial J}{\partial V}\Big|_{V \to 0}}.$$

(1.20)

Applying (1.20) to the equations of current for electron transport across the metal-semiconductor interface, we obtain the following set of functional dependencies for the specific contact resistance [7]:

1. Ohmic Contacts and Contact Resistance of Regrown GaInAs on InP

$$r_{c} \propto \begin{cases} \exp\left[\frac{\phi_{b}}{\sqrt{N_{D}}}\right] & \text{FE} \end{cases}$$

$$\exp\left[\frac{\phi_{b}}{\sqrt{N_{D}} \coth\left(\frac{E_{00}}{kT}\right)}\right] & \text{TFE}. \tag{1.21}$$

$$\exp\left[\frac{\phi_{b}}{kT}\right] & \text{TE}$$

The dependence of  $r_c$  on  $N_D$  is graphically summarized in Figure 1.5 [7].

Figure 1.5. Theoretical dependence of the specific contact resistance on the doping concentration.

## 1.4. Implementation of Regrown Contacts: Regrowth of GaInAs on InP

As an alternative to standard ohmic contacts achieved by deposition of metal on the semiconductor and subsequent alloying, non-alloyed contacts to highly doped regrown regions have been reported in the literature [8-10]. Non-alloyed ohmic contacts offer various advantages over alloyed contacts [11]. It is also possible to fabricate the source, drain and gate regions all with the same level of metalization since the alloying step is eliminated. This ease in the process

should improve reliability, uniformity and yield in device processing, which are parameters of great importance in, for example, the case of integrated circuits.

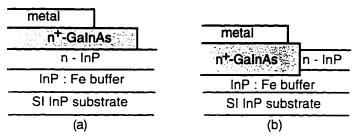

To demonstrate the feasibility of regrown contacts and establish the process basis, we characterize the regrowth of  $n^+$ -GaInAs on InP channel devices. We fabricate TLM patterns with both top and side regrowth as shown schematically in Figure 1.6. The basic structure consists of an Fe doped InP buffer grown on a semi-insulating InP substrate, which is followed by a 0.5 µm thick channel of Si doped InP ( $n = 2.4 \cdot 10^{17}$  cm<sup>-3</sup>). The structure in Figure 1.6 (a) is achieved as follows:  $Ga_{0.47}In_{0.53}As$  doped with Si  $(n = 1.24 \cdot 10^{18} \text{ cm}^{-3})$  is regrown on the original sample after the sample has been exposed to air. photoresist spinning and removal steps to simulate actual device processing conditions. Both the growth and the regrowth are done by MOCVD [12]. The sample is then patterned with a TLM mask by photolithography and metal liftoff. Standard AuGe/Ni/Au metalization scheme is used. The contact pads of the TLM patterns are 100 µm in length and 200 µm in width, and have spacings that vary from 3 µm to 30 µm. Finally, using the contact metal as the mask, the unmasked regrown areas are partially etched by reactive ion etching (CH<sub>4</sub>/H<sub>2</sub>/Ar gases with flows of 4/20/10 sccm, at a pressure of 75-125 mTorr, and a self dc bias of -500 V). Etching is completed by a 3:1:50 H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O solution, which etches away the regrown GaInAs and stops at the InP channel.

To get the structure in Figure 1.6 (b), first the TLM mask is used to pattern a 2000 Å thick SiO<sub>2</sub>, deposited by plasma enhanced chemical vapor deposition (PECVD). The InP channel is subsequently etched by RIE all the way to the buffer with conditions similar to above. The etching is completed by a wet etching step in a 3:1 HCl:H<sub>2</sub>O solution. Highly doped Ga<sub>0.47</sub>In<sub>0.53</sub>As is then selectively regrown in these regions in the MOCVD reactor. Afterwards, metal contacts are deposited on the regrown regions through the realignment of

Figure 1.6.(a) Schematic representation of (a) the top regrowth and (b) the side regrowth.

the TLM mask, photolithography, and subsequent metal liftoff. In both structures (a) and (b), adjacent TLM bars are isolated from one another by mesa etching.

In both cases, prior to regrowth, the wafer is treated with buffered HF to remove any nascent surface oxide. Also to test whether residual carbon compounds at the surface may have any effect on the electrical characteristics of the regrowth interface, some of the samples are placed in a UV ozone photoreactor to reduce the amount of residual carbon that might be present at the surface [13]. Along with some samples kept as non-annealed control samples, the process is completed by annealing the contacts using a strip annealer at 350°C, 400°C, and 450°C.

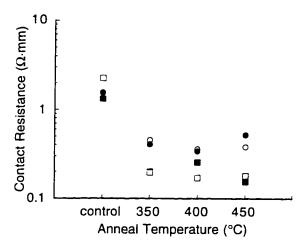

### 1.4.1. Measurements of Contact Resistance

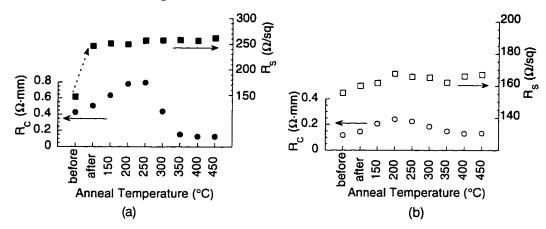

Once the structures have been fabricated, the room temperature contact resistances are measured by using a four probe measurement technique, in which the current is passed through two of the probes, and the potential difference is measured across the other two. This way, the effect of uncertainties in the definition of probe resistances is eliminated. For each data point, at least three different TLM patterns are measured and the average value is recorded. Figure 1.7 shows the variation of these contact resistances with respect to annealing temperature as measured at 300 K. The optimum annealing temperature for these structures appears to be around 400°C.

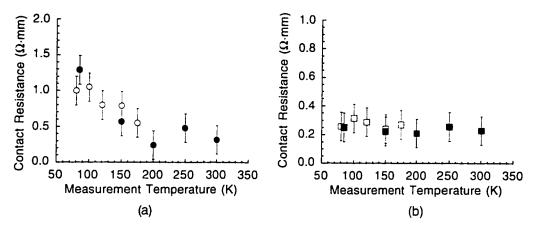

One of the main contributions to the contact resistance is from the regrown GaInAs to n-InP interface. To understand the effect of this interface better, we measure the contact resistances of annealed metal contacts on the regrown areas at low temperatures. Figure 1.8 shows the variations in these contact resistances with respect to the measurement temperature. Because of limited instrumental capabilities of the low temperature measurement system, these resistances were measured with two probes. The error bars on the graphs thus represent the uncertainties in defining the probe resistance. We see a temperature dependence in the contact resistance particularly in the top regrowth case.

Figure 1.7. Variation of the contact resistance with respect to annealing temperature for samples with top (circles) and side (squares) regrowth. UV ozone treatment of the samples before regrowth does not seem to have an appreciable effect on the resistance (solid markers show samples without any ozone treatment, unfilled markers show those with ozone treatment prior to regrowth).

Figure 1.8. The variation of the contact resistance for (a) the top regrowth, and (b) the side regrowth with respect to the measurement temperature (solid markers show samples without any ozone treatment, unfilled markers show those with ozone treatment prior to regrowth).

### 1.4.2. Experimental and Theoretical Calculation of the Interface Resistance

We notice that the case of top regrowth presents a two-layer conduction problem underneath the ohmic contact and can thus solve for the specific contact resistance associated with the GaInAs/InP interface,  $r_{ci}$ , by using the method

outlined in Section 1.2. In this case, the known variables are the metal to regrowth specific contact resistivity,  $r_c$ , the sheet resistance of the regrown GaInAs,  $R_{S2}$ , the sheet resistance of the InP channel,  $R_{SI}$ , and the measured contact resistance of the whole structure,  $R_C$ . The unknown variable is the specific contact resistivity of the regrowth to channel interface,  $r_{ci}$ . We determine the first three parameters from separate TLM measurements made on  $n^+$ -GaInAs and n-InP on semi-insulating InP substrates, where the growth and doping conditions of these layers are the same as those used for the actual experiments. For our structures these values are:  $r_c = 1.07 \cdot 10^{-7} \,\Omega \cdot \text{cm}^2$ ,  $R_{SI} = 220 \,\Omega/\text{sq}$  and  $R_{S2} = 21 \,\Omega/\text{sq}$ . From the four coupled nonlinear equations that we arrive as a result of the matrix manipulations, we calculate the numerical solutions using Mathematica [14]. We will refer to these solutions as "experimental values" henceforth.

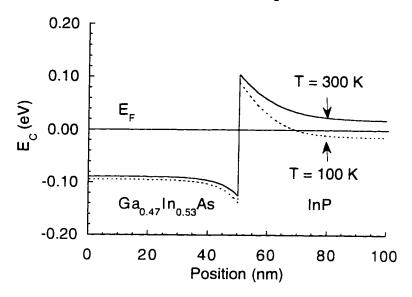

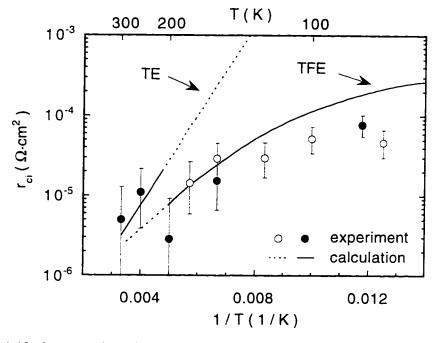

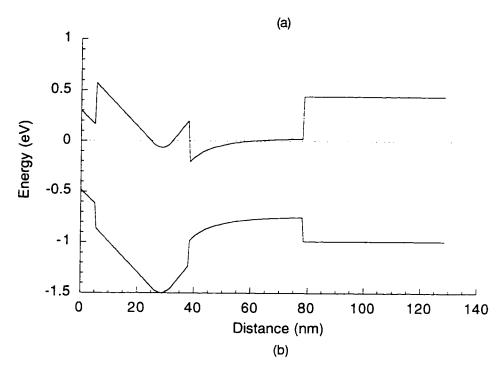

We also approach the problem theoretically by assuming an abrupt heterojunction interface between the regrown GaInAs and the n-InP channel by using the concepts outlined in Section 1.3, and model the measured resistivity by the effect of the conduction band barrier at this interface<sup>2</sup>. As we apply thermionic emission and thermionic field emission theories to electron transport across the GaInAs/InP barrier, we also check for the variation of the barrier height with respect to temperature by solving Poisson's equation at various temperatures [15]<sup>3</sup>. Figure 1.9 shows a sampling of these calculations. We note that the barrier height decreases by about 15 meV as the temperature moves down to 100K from 300K. Finally, we compare the  $r_{ci}$  values extracted from the experiments and those calculated by the theory in Figure 1.10. We note that the thermionic emission theory grossly overestimates the resistance below 200K. In this region, the resistance is well approximated by the thermionic field emission theory.

<sup>&</sup>lt;sup>2</sup> Although the methodology outlined in Section 3 is for a metal to semiconductor Schottky barrier interface, it should remain applicable to our case as well since the regrown GaInAs is doped highly degenerately.

In [15], the Fermi-Dirac integrals for the distribution of the electrons are approximated accurately by short series as outlined in [16, 17]. We have also solved the Poisson equation for this system using Joyce-Dixon approximation [18, 19], but found that the ratio of the electron concentration in the notch to the effective density of states  $(n/N_c)$  goes above 10 around T = 250 K, thereby limiting the range of applicability of this approximation to temperatures above this value.

Figure 1.9. Calculated conduction band edge for an abrupt GalnAs/InP heterointerface at T = 100 K and 300 K.

Figure 1.10. A comparison between the theoretical and the experimental values (obtained by circuit analysis) for the specific contact resistivity,  $r_c$ , for the top regrowth. The solid lines indicate the regions where the calculations are valid according to [6, 7] (solid markers show samples without any ozone treatment, unfilled markers show those with ozone treatment prior to regrowth).

## 1.5. Summary

We have reviewed the existing methods that are used to characterize ohmic contacts and introduced a new one to analyze contacts into which the current conduction takes place in two layers. We have also established a regrowth process in which  $n^+$ -GaInAs was grown on n-InP channel devices. By measuring the contact resistance at various temperatures on annealed samples, we modeled the variation of the interfacial specific contact resistivity by thermionic field emission and thermionic emission theories as applied to the electron transport across the heterojunction barrier. Using the 2-layer TLM method, we also solved for the contact resistivity based on experimental measurements and showed good agreement between theoretical predictions and the experimental data.

#### References

- [1] D.C. Look, Electrical characterization of GaAs materials and devices, Chapter 2.1. Chichester: Wiley, 1989.

- [2] R.E. Williams, Modern GaAs processing methods, Chapter 11. Boston: Artech House, 1990.

- [3] H.H. Berger, "Models for contacts to planar devices," *Solid-State Electronics*, vol. 15, pp. 145-58, 1972.

- [4] G. Gonzalez, Microwave transistor amplifiers: analysis and design, pp. 24-25. Englewood Cliffs, N.J.: Prentice-Hall, 1984.

- [5] S.M. Sze, *Physics of semiconductor devices*, 2nd ed, Chapter 5. New York: Wiley, 1981.

- [6] F.A. Padovani and R. Stratton, "Field and themionic-field emission in Schottky barriers," *Solid-State Electronics*, vol. 9, pp. 695-707, 1966.

- [7] A.Y.C. Yu, "Electron tunneling and contact resistance of metal-silicon contact barriers," *Solid-State Electronics*, vol. 13, pp. 239-47, 1970.

- [8] H. Shimawaki, N. Furuhata, and K. Honjo, "Ohmic contacts to p-GaAs with p<sup>+</sup>/p regrown structures formed by metalorganic molecular beam epitaxy," *Journal of Applied Physics*, vol. 69, pp. 7939-41, 1991.

- [9] A. Palevski, P.M. Solomon, T.F. Kuech, M. Tischler, and C. Umbach, "Selectively regrown contacts to field-effect transistors with twodimensional electron-gas channels," *IEEE Electron Device Letters*, vol. 11, pp. 535-7, 1990.

- [10] A. Palevski, P. Solomon, T.F. Kuech, and M.A. Tischler, "Regrown ohmic contacts to thin GaAs layers and two-dimensional electron gas," *Applied Physics Letters*, vol. 56, pp. 171-3, 1990.

- [11] J.B. Shealy, M.M. Hashemi, K. Kiziloglu, S.P. DenBaars, U.K. Mishra, T.K. Liu, J.J. Brown, and M. Lui, "High-breakdown-voltage AlInAs/GaInAs junction-modulated HEMT's (JHEMT's) with regrown ohmic contacts by MOCVD," *IEEE Electron Device Letters*, vol. 14, pp. 545-7, 1993.

- [12] M.M. Hashemi, J.B. Shealy, S.P. DenBaars, and U.K. Mishra, "High-speed p<sup>+</sup> GaInAs-n InP heterojunction JFET's (HJFET's) grown by MOCVD," *IEEE Electron Device Letters*, vol. 14, pp. 60-2, 1993.

- [13] R.F. Kopf, A.P. Kinsella, and C.W. Ebert, "A study of the use of ultraviolet-ozone cleaning for reduction of the defect density on molecular beam epitaxy grown GaAs wafers," *Journal of Vacuum Science* &

- Technology B (Microelectronics Processing and Phenomena), vol. 9, pp. 132-5, 1991.

- [14] S. Wolfram, Mathematica: a system for doing mathematics by computer, 2nd ed, Redwood City, Calif.: Addison-Wesley Pub. Co., Advanced Book Program, 1991.

- [15] W.R. Frensley, "Development of an interactive design environment for heterostructure and quantum-well devices," *IEEE Transactions on Electron Devices*, vol. 38, pp. 2704-5, 1991.

- [16] P. Van Halen and D.L. Pulfrey, "Accurate, short series approximations to Fermi-Dirac integrals of order -1/2, 1/2, 1, 3/2, 2, 5/2, 3, and 7/2," *Journal of Applied Physics*, vol. 57, pp. 5271-4, 1985.

- [17] P. Van Halen and D.L. Pulfrey, "Erratum: "Accurate, short series approximations to Fermi-Dirac integrals of order -1/2, 1/2, 1, 3/2, 2, 5/2, 3, and 7/2" [J. Appl. Phys. 57, 5271 (1985)]," Journal of Applied Physics, vol. 59, pp. 2264, 1986.

- [18] G.L. Snider, I.-H. Tan, and E.L. Hu, "Electron states in mesa-etched one-dimensional quantum well wires," *Journal of Applied Physics*, vol. 68, pp. 2849-5, 1990.

- [19] H. Kroemer, "Analytic approximations for degenerate accumulation layers in semiconductors, with applications to barrier lowering in isotype heterojunctions," *Journal of Applied Physics*, vol. 52, pp. 873-8, 1981.

## Chapter 2

# Effects of Rapid Thermal Annealing on Bulk AlInAs/InP and AlInAs/GaInAs/InP HEMT Structures with Planar Si Doping

AlInAs/GalnAs/InP high electron mobility transistors (HEMT) have proven to be one of the best candidates for low-noise microwave and millimeter wave applications [1]. Two of the main factors influencing the performance of these devices are the total two-dimensional electron gas concentration (2DEG) and the corresponding mobility. Improvements in the high-frequency performance of these devices can be achieved by the reduction of external parasitics through self-aligned gate technology in which the source and drain ohmic regions are fabricated by ion implantation. The HEMT structure then has to be annealed to activate the implanted ions. The key concerns are what happens to the device structure and its electrical properties during the high temperature anneals, and particularly how the sheet carrier concentration and the mobility are affected.

Previous studies have investigated layer interdiffusion characteristics of AlGaAs/GaAs quantum well heterostructures [2], and GaInAs/AlInAs quantum wells [3] under annealing with SiO<sub>2</sub> capping. The effects of rapid thermal annealing on the integrity of GaInAs/AlInAs interfaces [4], pseudomorphic AlGaAs/InGaAs/GaAs HEMTs [5], selectively doped GaAs/n-AlGaAs heterostructures [6], and modulation-doped AlGaAs/GaAs heterostructures [7] have also been studied.

In this chapter, we investigate the effects of high temperature rapid thermal annealing (RTA) processes on carrier concentration and mobility of bulk AlInAs and lattice-matched AlInAs/GaInAs/InP HEMT structures with planar Si doping. We observe both deterioration in the mobility of the HEMT samples and loss of charge with annealing. We show that the influencing factors for these observations are the surface and the heterointerface. We note particularly that the bulk AlInAs stays stable even at high annealing temperatures such as 900°C.

## 2.1. Experiments

The cross sections of the planar doped AlInAs and the AlInAs/GaInAs/InP HEMT structures are shown in Figure 2.1. The planar-doped AlInAs structure simulates the donor region of the HEMT and is employed to

investigate the effects of RTA processes on the bulk AlInAs region only, separate from the effects on the AlInAs/GaInAs heterointerface. These structures were grown by MBE, lattice-matched to semi-insulating InP substrate. The room temperature net carrier concentration  $(n_s)$  and mobility  $(\mu)$  of the bulk AlInAs were 5.4·10<sup>12</sup> cm<sup>-2</sup> and 840 cm<sup>2</sup>/V·sec respectively. The HEMT structure had a net carrier concentration and mobility of 3.1·10<sup>12</sup> cm<sup>-2</sup> and 8500 cm<sup>2</sup>/V·sec at 300K and 3.0·10<sup>12</sup> cm<sup>-2</sup> and 26,500 cm<sup>2</sup>/V·sec at 15K respectively. The HEMT samples were rapid thermal annealed for 5 s at 700°C, 800°C, and 900°C in a forming gas ambient (10% H<sub>2</sub>, 90% N<sub>2</sub>) in an AG Associates Heatpulse 410 rapid thermal annealer. The choices for the capping material to prevent As desorption were  $Si_3N_4$  (n = 2.05 : 1000 Å),  $SiO_2$  (n = 1.47 : 1000 Å) and GaAs pieces in close proximity. The Si<sub>3</sub>N<sub>4</sub> and the SiO<sub>2</sub> caps were deposited by a plasma enhanced chemical vapor deposition (PECVD) system; the thicknesses and the refractive indices of the films were measured by an ellipsometer. The indices obtained show that the composition of the dielectric films are very close to being stoichiometric. The temperature dependence of the mobility and the sheet carrier concentration of the samples were measured by a Van der Pauw technique.

#### 2.2. Results and Discussions

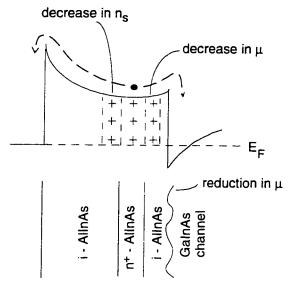

Figure 2.2 depicts a schematic diagram of possible effects of high temperature anneals on the device structure, such as diffusion of the donor Si atoms and the intermixing of the AlInAs/GaInAs heterointerface, and their resulting influence on the electrical properties of the structure, such as  $\mu$  and  $n_s$ .

| GalnAs | Contact n = 5x | 18 -3<br>k10 cm 70 Å |                               |            |        |

|--------|----------------|----------------------|-------------------------------|------------|--------|

| AllnAs | Schottky       | 200 Å                |                               |            |        |

| AlinAs | Donor $n = 1x$ | 10 cm 33 Å           |                               |            |        |

| AllnAs | Spacer         | 15 Å                 |                               |            |        |

| GainAs | Channel        | 400 Å                | GalnAs                        | Cap        | 15 Å   |

| AllnAs | 4-Period       | 400 Å                | AlinAs                        |            | 1000 Å |

| GalnAs | Superlattice   |                      |                               | δ - doping |        |

| AllnAs | Buffer         | 2500 Å               | AllnAs                        |            | 4000 Å |

| InP    | Semi Insulatin | ng Substrate         | InP Semi Insulating Substrate |            |        |

|        | (a)            |                      |                               | (b)        |        |

Figure 2.1.(a) AllnAs/GalnAs/InP HEMT and (b)  $\delta$ -doped bulk AllnAs structures used in this study.

Figure 2.2. Possible effects of high temperature anneals on the device structure and its electrical properties.

We now discuss these effects starting with the mobility and the carrier concentration characteristics after the 700°C and 800°C anneals. We continue with the 900°C anneals in a separate section as these characteristics differ significantly from the previous ones.

### 2.2.1. 700°C and 800°C Anneals

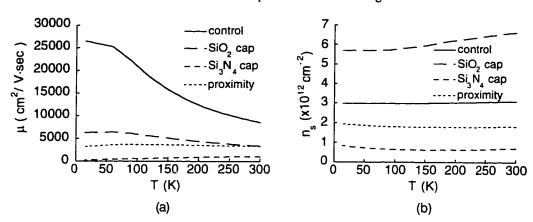

### 2.2.1.1. Discussions on the Mobility

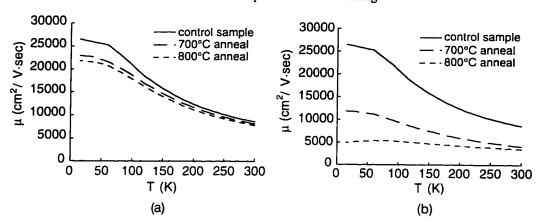

Anneals carried out on samples with Si<sub>3</sub>N<sub>4</sub> capping or GaAs pieces in close proximity result in similar mobility versus temperature characteristics. In both of these methods, a slight reduction in mobility is observed as the annealing temperature increases. Figure 2.3 shows the mobility versus temperature measurements for the samples annealed with GaAs in proximity and SiO<sub>2</sub> capping. We suggest that the reduction in the mobilities is due to the enhanced diffusion of the Si donor atoms towards the 2 DEG channel, which increases the coulombic scattering between the carriers and the ionized donors.

#### 2. Effects of Rapid Thermal Annealing

Figure 2.3. Comparison of mobility vs. temperature between (a) proximity and (b) SiO<sub>2</sub> capped anneals.

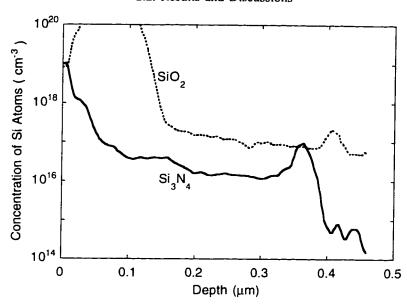

We also observe in Figure 2.3 that the reduction in mobilities of the samples annealed with SiO<sub>2</sub> capping is more pronounced than that of the samples annealed with proximity GaAs. We note that the reduction in the low temperature mobilities is as high as 80% as compared to their original value. This further reduction in mobility in the SiO<sub>2</sub> capped samples may be attributed to the diffusion of Ga and In atoms into the oxide, which results in vacancies and the intermixing of the AlInAs/GaInAs interface. To check this phenomenon, secondary ion mass spectroscopy (SIMS) profiling was carried out on samples that had been annealed using Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub> caps. Since the mobility versus temperature behavior is very similar for the anneals done with proximity GaAs and Si<sub>3</sub>N<sub>4</sub> capping, we only compare the SIMS data between samples annealed using SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>.

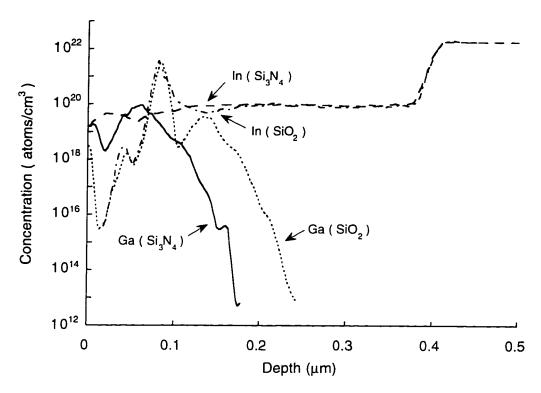

Prior to profiling, the Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub> caps were removed in solutions of concentrated HF and buffered oxide etch respectively. The outdiffusion of Ga and In atoms for the SiO<sub>2</sub> capped anneals is apparent from Figure 2.4, which shows the SIMS profiles for Ga and In atoms for the samples annealed at 800°C with Si<sub>3</sub>N<sub>4</sub> and SiO<sub>2</sub> capping. The layer interdiffusion phenomenon has previously been used for wavelength modification of quantum wells [2, 3]. The outdiffusion of Ga atoms in rapid thermal annealing processes with SiO<sub>2</sub> encapsulation has been also previously shown to occur in bulk GaAs [8].

Figure 2.4. Normalized SIMS profiles showing a comparison of Ga and In concentrations in HEMT samples with  $SiO_2$  and  $Si_3N_4$  capped anneals at 800°C.

## 2.2.1.2. Discussions on the Carrier Concentration

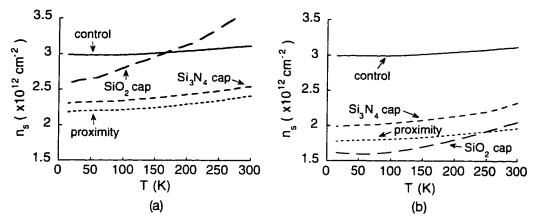

Figure 2.5 shows the carrier concentration  $(n_s)$  versus temperature for 700°C and 800°C anneals done with  $Si_3N_4$  and  $SiO_2$  cappings, and GaAs in close proximity. A decrease in  $n_s$  with increasing annealing temperatures is observed. There may be a few possible reasons for this reduction in the charge concentration:

- (i) Electron capture by defects that could possibly be generated during the high temperature anneals.

- (ii) Possible amphoteric behavior of Si in AlInAs similar to as observed before in AlGaAs [7].

- (iii)Preferential vacancy enhanced diffusion of the Si donor atoms towards the surface, which would both reduce the efficiency of electron transfer to the channel and also could form electrically inactive Si complexes.

#### 2. Effects of Rapid Thermal Annealing

Figure 2.5. Carrier concentrations vs. temperature for samples annealed with  $SiO_2$  and  $Si_3N_4$  caps, and proximity GaAs, at annealing temperatures of (a) 700°C and (b) 800°C.

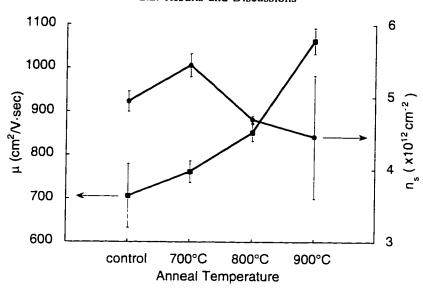

To determine the dominant cause of the reduction of sheet carrier concentration, the  $\delta$ -doped bulk AlInAs samples shown in Figure 2.1 (b) were subjected to the same annealing temperatures and conditions as the HEMT samples. Figure 2.6 shows the measurement results for anneals done with Si<sub>3</sub>N<sub>4</sub> encapsulation. We note that the electron concentrations are maintained to within experimental errors, and the mobility actually increases with the annealing temperature. Cathodoluminescence (CL) studies of bulk AlInAs samples also show a much higher intensity for AlInAs at 900°C than at 700°C indicating an improvement in the bulk AlInAs quality. The CL spectra are shown in Figure 2.7. These findings suggest that electron capture by defects is not the reason for the loss of carriers with annealing since the bulk AllnAs stays stable during annealing. Amphoteric behavior of Si in AlInAs is also ruled out since, to within experimental errors, the 2 DEG carrier concentration does not vary with respect to annealing. Previous work has shown that the AlInAs/GaInAs interface preserves its quality during anneals of up to 800°C [4]. We therefore believe that surface enhanced diffusion of the Si donor atoms is the dominant mechanism for the loss of charge in the HEMT structures. As depicted in Figure 2.2, and evidenced by the reduction in mobility as discussed in Section 2.2.1.1, there appears to be a diffusion of the donor atoms towards the channel as well. However, the surface enhanced diffusion seems to dominate, resulting in an overall decrease in the measured sheet carrier concentration.

Figure 2.6. Room temperature mobility and carrier concentration values for the  $\delta$ -doped bulk AllnAs sample for different annealing temperatures. Si<sub>3</sub>N<sub>4</sub> capping was used during the annealing. Error bars show experimental variations in the measurements.

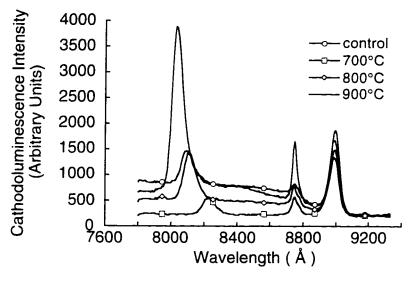

Figure 2.7.CL spectra of bulk AllnAs for samples after 700°C, 800°C, and 900°C anneals.

#### 2. Effects of Rapid Thermal Annealing

Figure 2.8. (a) Mobility and (b) sheet carrier concentration measurements vs. temperature for 900°C anneals.

#### 2.2.2. 900°C Anneals

Figure 2.8 shows mobility and sheet carrier concentration data for samples annealed at 900°C using  $Si_3N_4$  and  $SiO_2$  caps, and GaAs in close proximity. We note that the mobility for the samples show a considerable reduction for all three methods of annealing. Another point of observation is that the mobility becomes virtually independent of the measurement temperature. The carrier concentration drops to about  $1.7 \cdot 10^{12}$  and  $6 \cdot 10^{11}$  cm<sup>-2</sup> for the proximity and  $Si_3N_4$  anneals, but actually increases to  $6 \cdot 10^{12}$  cm<sup>-2</sup> for the anneal with  $SiO_2$  cap. The dramatic reduction in the mobilities and its temperature independence is believed to be caused by severe layer mixing at the AlInAs/GaInAs interface, and a loss of the crystalline properties of the structure, which occurs only at or above 900°C.

The increase in the sheet charge concentration for the SiO<sub>2</sub> anneal is due to the doping of the ternary materials by Si back-diffusing from the SiO<sub>2</sub> cap [3]. We observe this behavior also by the SIMS measurements as shown in Figure 2.9. Here, we see that there is a definite increase in the surface Si concentration in the sample annealed with a SiO<sub>2</sub> cap at 900°C compared to the sample annealed with a Si<sub>3</sub>N<sub>4</sub> cap at 800°C. We should note that SIMS data of Si distribution for an anneal done with a Si<sub>3</sub>N<sub>4</sub> cap at 700°C look similar to the 800°C anneal. We also expect the Si distribution in the samples annealed using Si<sub>3</sub>N<sub>4</sub> caps to be qualitatively close to the non-annealed sample. In this regard, SIMS measurements done on similar heterostructures with bulk doping of AlInAs were reported to show no extensive movement of Si dopants under similar annealing conditions [9].

Figure 2.9. Normalized SIMS profiles for Si for anneals done with Si<sub>3</sub>N₄ cap (at 800°C) and SiO₂ cap (at 900°C).

#### 2.3. Summary

This study shows that the heterostructure integrity of the AlInAs/GaInAs interface is destroyed after a 900°C anneal even though the material quality of bulk AlInAs improves at this temperature. Also, a loss of carriers to surface states by vacancy enhanced diffusion in samples annealed at 700°C and 800°C are observed. The mobility in these samples also degrades with increasing annealing temperature due to diffusion of the donor Si atoms towards the 2 DEG channel. For the particular case of anneals with SiO<sub>2</sub> encapsulation, the reduction in mobility is more pronounced due to the outdiffusion of Ga and In atoms into the oxide thereby creating vacancies and resulting in interface intermixing.

The reduction in mobility and charge loss are more significant at low temperatures. We therefore conclude that ohmic contact formation by dopant implantation and activation is not a viable method particularly for applications which require stable device characteristics not only at room temperatures, but at cryogenic temperatures as well.

#### References

- [1] U.K. Mishra, A.S. Brown, and S.E. Rosenbaum, "DC and RF performance of 0.1 μm gate length Al<sub>0.48</sub>In<sub>0.52</sub>As-Ga<sub>0.38</sub>In<sub>0.62</sub>As pseudomorphic HEMTs," International Electron Devices Meeting, Technical Digest, pp. 180-3, 1988.

- [2] M.D. Camras, N.J. Holonyak, R.D. Burnham, W. Streifer, D.R. Scifres, T.L. Paoli, and C. Lindstrom, "Wavelength modification of Al<sub>x</sub>Ga<sub>1-x</sub>As quantum well heterostructure lasers by layer interdiffusion," *Journal of Applied Physics*, vol. 54, pp. 5637-41, 1983.

- [3] S. O'Brien, J.R. Shealy, V.K.F. Chia, and J.Y. Chi, "Selective interdiffusion of GaInAs/AlInAs quantum wells by SiO<sub>2</sub> encapsulation and rapid thermal annealing," *Journal of Applied Physics*, vol. 68, pp. 5256-61, 1990.

- [4] Y.-P. Hu, P.M. Petroff, X. Qian, and A.S. Brown, "Substrate misorientation effects on the structure and electronic properties of GaInAs-AlInAs interfaces," *Applied Physics Letters*, vol. 53, pp. 2194-6, 1988.

- [5] D.C. Streit, W.L. Jones, L.P. Sadwick, C.W. Kim, and R.J. Hwu. "Effect of rapid thermal annealing on planar-doped pseudomorphic InGaAs high electron mobility transistor structures," *Applied Physics Letters*, vol. 58, pp. 2273-5, 1991.

- [6] S. Tatsuta, T. Inata, S. Okamura, and S. Hiyamizu, "The effects of tungstenhalogen lamp annealing on a selectively doped GaAs/N-AlGaAs heterostructure grown by MBE," *Japanese Journal of Applied Physics, Part 2* (*Letters*), vol. 23, pp. L147-9, 1984.

- [7] P. Pearah, T. Henderson, J. Klem, H. Morkoc, B. Nilsson, O. Wu, A.W. Swanson, and D.R. Ch'en, "Rapid thermal annealing of modulation-doped Al<sub>x</sub>Ga<sub>1-x</sub>As/GaAs heterostructures for device applications," *Journal of Applied Physics*, vol. 56, pp. 1851-5, 1984.

- [8] M. Katayama, Y. Tokuda, Y. Inoue, A. Usami, and T. Wada, "Ga out-diffusion in rapid-thermal-processed GaAs with SiO<sub>2</sub> encapsulants," *Journal of Applied Physics*, vol. 69, pp. 3541-6, 1991.

- [9] M.A. Tischler, B.D. Parker, J. DeGelormo, T.N. Jackson, F. Cardone, and M.S. Goorsky, "Thermal stability of MBE-grown Si-doped InGaAs/InAlAs heterostructures," *Conference Proceedings, Third International Conference on Indium Phosphide and Related Materials*, pp. 602-5, 1991.

# Chapter 3

# Regrowth of n<sup>+</sup> GaInAs on GaInAs Channel Devices

Obtaining reliable and low resistance ohmic contacts is one of the enabling factors in reducing device parasitics and achieving high frequency and low noise transistors. We previously stated that possible approaches that can be taken to realize low resistance contacts in high performance HEMTs are: (a) ion implantation, (b) capping with a highly doped low bandgap material, and (c) highly doped epitaxial regrowth of contacts. The ion implantation method requires a high temperature, post-implantation anneal to activate the implanted dopants. However, as has been observed in Chapter 2, this annealing step gives rise to problems of mechanical, electrical and metallurgical stability of the underlying structure [1] and therefore is not a very desirable technology for reliable contacts. The second method has been investigated by some researchers [2], but since it provides a tunneling contact, its applications are limited to materials with small bandgaps and high doping incorporability. Regrown ohmic contacts, however, have the potential to enable low resistance, non-alloyed, and reliable contacts to the channels of FETs for various material systems [3-5]. For power applications, JHEMT structures incorporating regrown source and drain contacts have been shown to have higher breakdown voltages compared to control devices fabricated with alloyed ohmic contacts [4]. In Chapter 1, we presented initial technological and theoretical work on the regrowth of GaInAs on InP channel devices. In this chapter, we advance the state-of-the-art by investigating highly doped regrown GaInAs ohmic contacts to various FET structures with GaInAs channels and report on a technology with which we have achieved temperature stable regrown contacts with contact resistances of 0.1  $\Omega$ ·mm.

#### 3.1. Fabrication of the TLM Patterns

To characterize the ohmic contact resistance of the regrown contacts, we use transmission line patterns as shown in Figure 1.2. The TLM pads have dimensions of  $100 \times 200 \, \mu m^2$ , and seven separations ranging from 3 to  $30 \, \mu m$ . The process to fabricate the structures starts with PECVD SiO<sub>2</sub> deposition on the samples and photolithography to define the pads. We then etch the TLM patterns in the oxide by either a CF<sub>4</sub> plasma or an SF<sub>6</sub> / Ar RIE and do a short clean-up in a diluted buffered HF acid solution (BHF). We subsequently etch the desired amount of the semiconductor in a 3:1:50 solution of  $H_3PO_4:H_2O_2:H_2O$ . We then

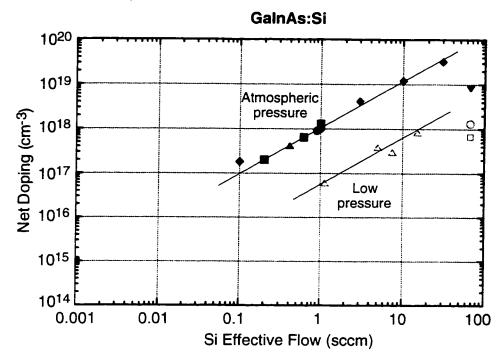

dip the samples in BHF, and after rinsing with water, transfer them into the MOCVD reactor immediately for regrowth. The samples themselves are grown by MBE.

Before the regrowth starts, the samples are kept at  $200^{\circ}$ C for 5 minutes with  $H_2$  flow, and then baked at  $450^{\circ}$ C under tertiary butylarsine (TBA) overpressure. Regrowth takes place at  $620^{\circ}$ C with TBA, trimethylgallium (TMG) and trimethylindium (TMIn) precursors. Disilane ( $Si_2H_6$ ) is used for Si doping of the regrown GaInAs. The growth occurs selectively on the etched surfaces over the masked areas since the operating pressure is kept at 0.1 atm.

In the standard process, after the regrowth is done, we remove the  $SiO_2$  mask by dipping the samples in BHF  $^1$ . We then metalize the contacts by photolithography and liftoff (AuGe/Ni/Au is used), and complete the process by mesa etching of the TLM bars.

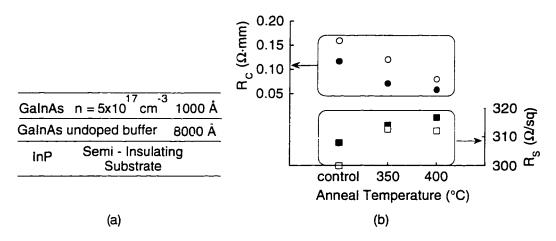

### 3.2. Initial Regrowth Studies on FET and HEMT Structures

To establish the regrowth technology, we carry out our first study of GaInAs homojunction regrowth on a simple doped channel structure that

Figure 3.1.(a) The GalnAs doped-channel structure and (b) the contact  $(R_c)$  and sheet  $(R_s)$  resistances for regrown contacts on this structure vs. annealing temperature. Solid markers depict top regrowth, open markers depict side regrowth.

<sup>&</sup>lt;sup>1</sup> A modified procedure to ensure stable contacts is discussed later in the chapter.

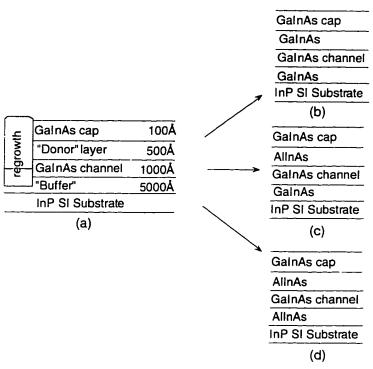

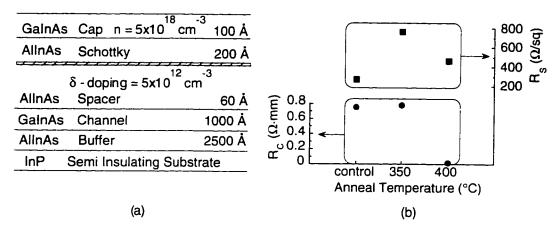

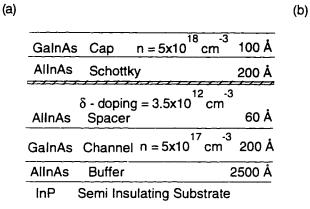

Figure 3.2. Layer schematics used to investigate the effects of implementing regrowth on AllnAs containing HEMT structures. The dashed line in the "regrowth" area show the possibilities of starting the regrowth either from the GalnAs channel, or from the AllnAs buffer. The figures represent the following:

- (a) the structure on which regrowth is desired.

- (b) the starting "all GalnAs" structure.

- (c) top GalnAs layer is replaced by AllnAs.

- (d) GalnAs buffer is replaced by AlInAs.

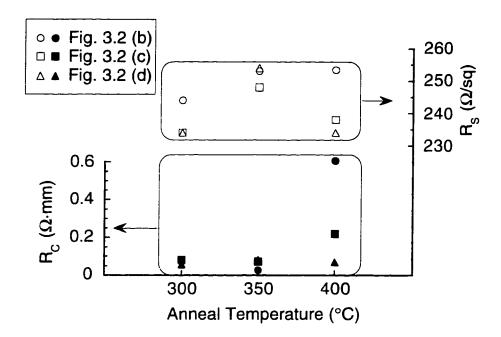

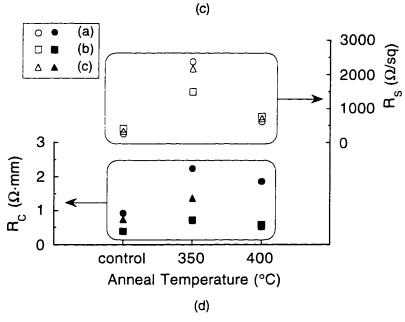

comprises of an 8000 Å thick  $Ga_{0.47}In_{0.53}As$  buffer layer grown lattice matched on semi-insulating InP substrate, on top of which is a 1000 Å thick GaInAs "channel" region with  $n = 5 \cdot 10^{17}$  cm<sup>-3</sup> doping. We examine both top and side regrown contacts on this device structure similar to what is done in Chapter 1. Figure 3.1 shows the contact  $(R_C)$  and sheet resistances  $(R_S)$  of these regrown contacts with respect to the annealing temperature. The annealing is carried out on a strip annealer under forming gas atmosphere. We observe low resistance regrown ohmic contacts from this "homojunction" regrowth. Our goal is to implement this regrowth technology in high-performance HEMTs. Thus, we next carry out a set of experiments that guides us in that direction. Figure 3.2 shows the evolution of the structures that we use to do the transition from the structure of Figure 3.1 to a

Figure 3.3. Contact and sheet resistances for the structures shown in Figure 3.2. Open markers depict the  $R_{\rm s}$ , solid markers depict the  $R_{\rm c}$  values. Low resistance regrowth is achieved on all structures.

standard HEMT structure. Notice that going from (b) to (d), we incorporate an AlInAs layer at each step, eventually arriving at (d) that mimics a HEMT structure. Because the process is an ex-situ etch and regrowth process, the reason for this experiment is to find out whether the incorporation of Al containing layers in the underlying structure for regrowth presents problems for the regrowth itself. Clearly, when we etch into the sample as shown in Figure 3.2 (a), we expose the AlInAs donor layer on the side. This might result in the creation of interface traps and charge depletion from the channel thereby yielding a high contact resistance. If the etch is done into the buffer, then the regrowth has to be initiated on an exposed and oxidized AlInAs surface. Note that in all of these structures, the GaInAs channel is doped to  $n = 5 \cdot 10^{17}$  cm<sup>-3</sup>. Figure 3.3 shows the extracted contact and sheet resistances from TLM measurements for the n<sup>+</sup> GaInAs regrowths done on these structures. For all cases, we achieve low contact resistances, and the samples are thermally stable up to annealing temperatures of  $400^{\circ}C$ .

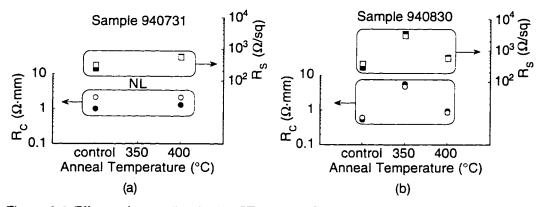

Figure 3.4.(a) The HEMT structure used and (b) the effects of annealing on the TLM resistances for regrown contacts on it. Note the jump in the R<sub>s</sub> when sample is annealed.

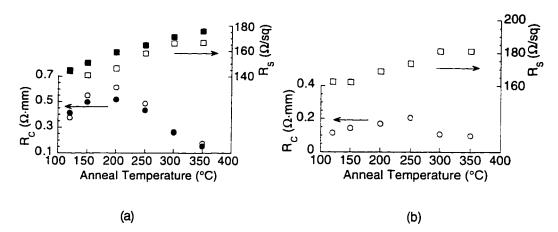

Having established the basis of the process, we experiment with regrowth on an actual HEMT sample with a  $\delta$ -doping (  $n_s = 5.10^{12} \text{ cm}^{-2}$  ) in the AlInAs carrier supply layer. Similar to the previous structures, we keep the channel thickness at 1000 Å. Figure 3.4 shows the effects of annealing on these contacts. We note a significant increase in the extracted sheet resistance when the structure is annealed. This result is somewhat surprising because in all previous regrowths on structures mimicking HEMTs, the contacts have shown thermal stability. The current structure, however, has two differences from the previous ones: (i) the GaInAs channel is undoped, and (ii) the AIInAs layer has Si doping in it. To address the question of whether lack of doping in the GaInAs channel is detrimental to low resistance contact regrowth, we design two doped-channel HEMT structures. Figure 3.5 shows the effect of annealing on the TLM resistances for regrown contacts on these structures. Note that we try both δdoping and uniform doping in the GaInAs channel, and design the doping concentrations in the channel and the AlInAs donor layers such that approximately two thirds of the charge comes from the AlInAs layer. Observing the fact that the extracted sheet resistances for all three structures again increase substantially with annealing, we can conclude that doping in the GalnAs channel itself is not a determining factor for the temperature instability of these contacts. In a separate experiment, we also look at the uniformly doped sample more closely. and heat it up with 50°C increments starting from 150°C. The deterioration in the TLM resistances actually seem to be starting around 250°C.

| Cap n = 5x10            | <sup>18</sup> cm <sup>-3</sup> 140 Å                     |

|-------------------------|----------------------------------------------------------|

| Schottky                | 200 Å                                                    |

| $\delta$ - doping = 5x1 | 12 -3<br>0 cm                                            |

| Spacer                  | 60 Å                                                     |

| Channel                 | 200 Å                                                    |

| Buffer                  | 2500 Å                                                   |

| Semi Insulating         |                                                          |

|                         | Schottky Schottky δ - doping = 5x1 Spacer Channel Buffer |

| GalnAs | Cap $n = 5x10^{18}$ cm    | <sup>3</sup> 100 Å |

|--------|---------------------------|--------------------|

| AlinAs | Schottky                  | 200 Å              |

| δ-     | doping = 3.5x10 cm        | -3                 |

| AllnAs | Spacer                    | 60 Å               |

| δ-0    | $doping = 1.5x10^{12} cm$ | <sup>3</sup> 150 Å |

| GalnAs | Channel                   | 50 Å               |

| AlinAs | Buffer                    | 2500 Å             |

| InP S  | Semi Insulating Substr    | ate                |

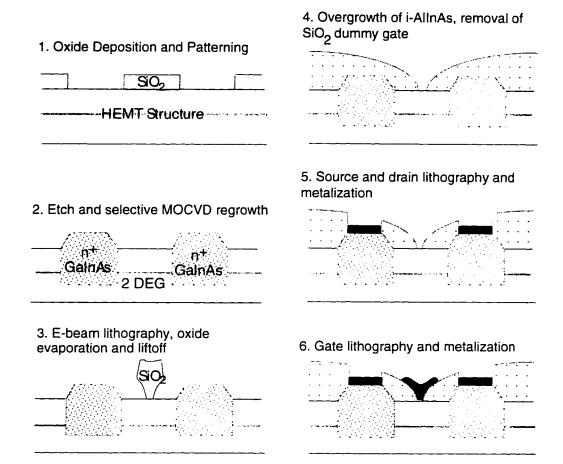

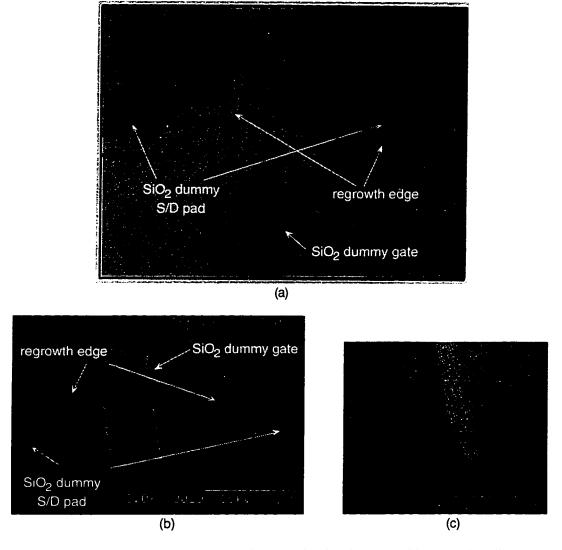

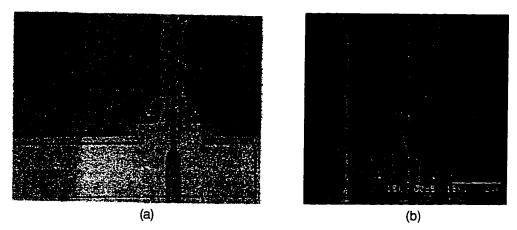

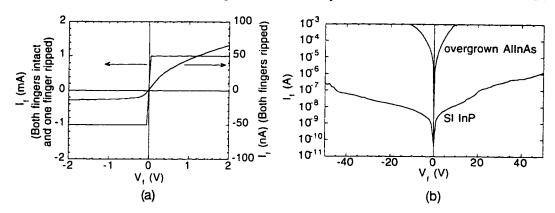

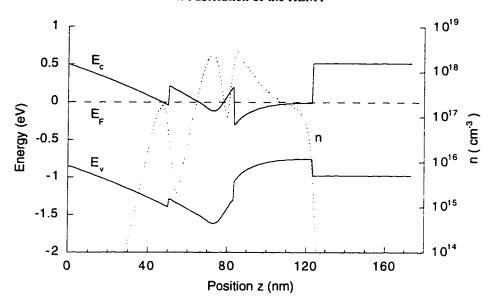

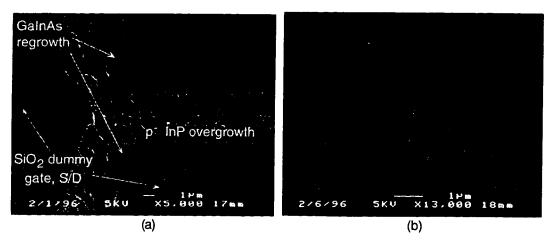

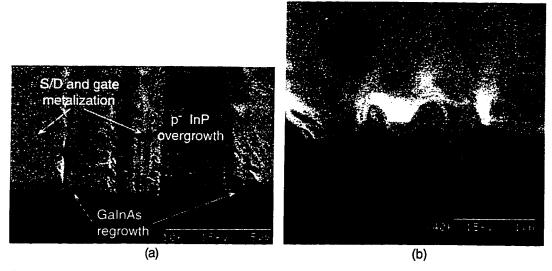

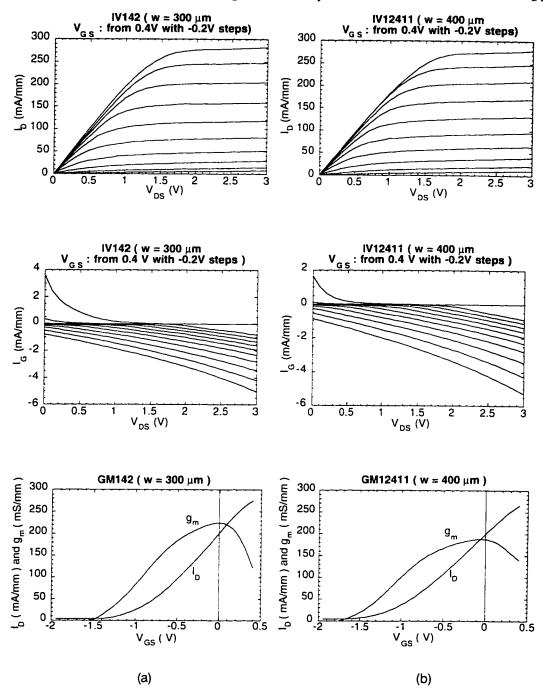

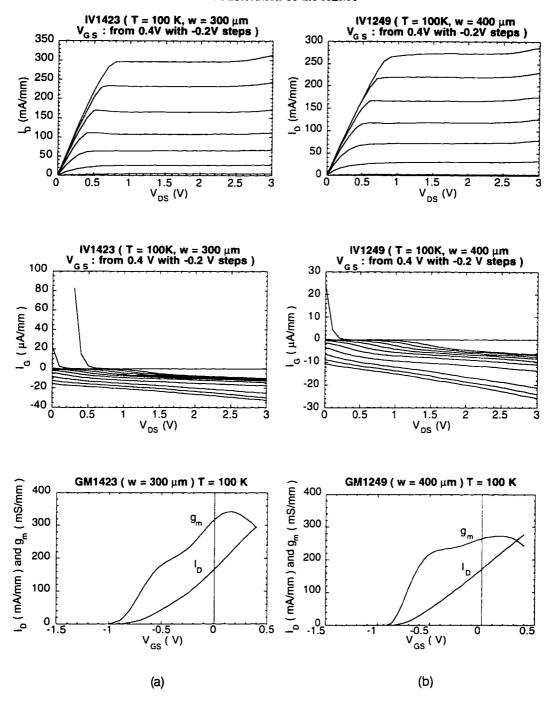

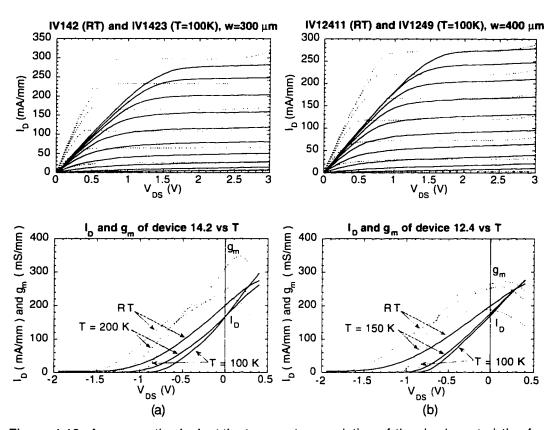

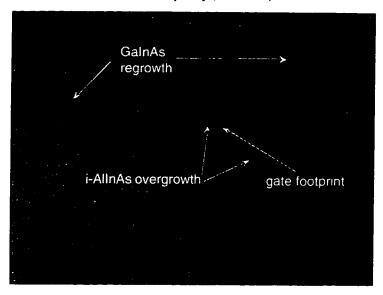

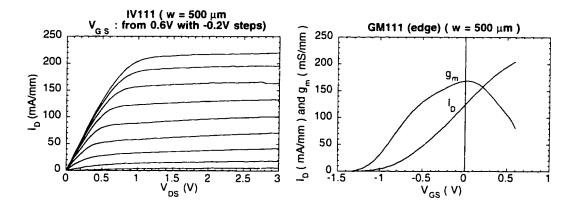

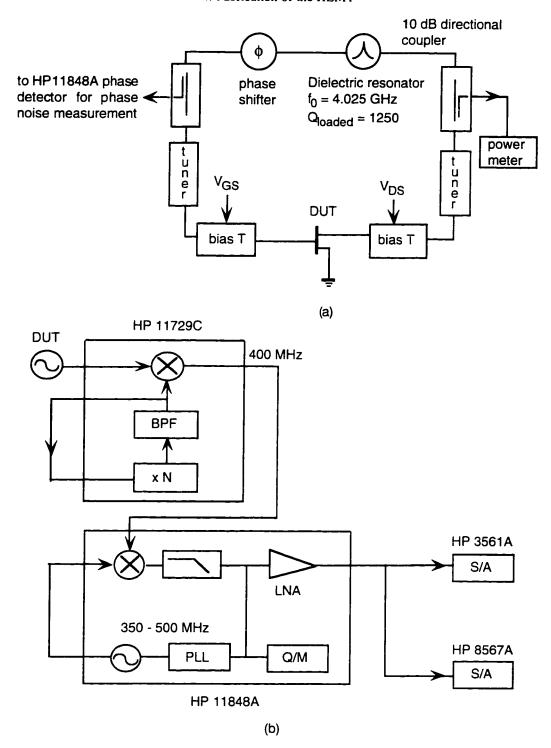

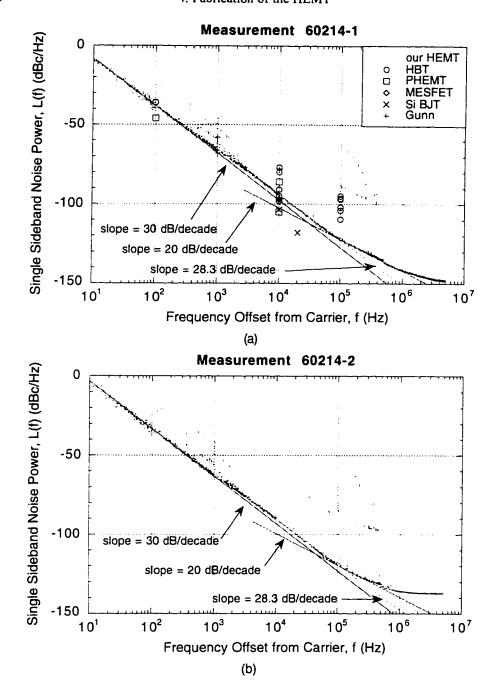

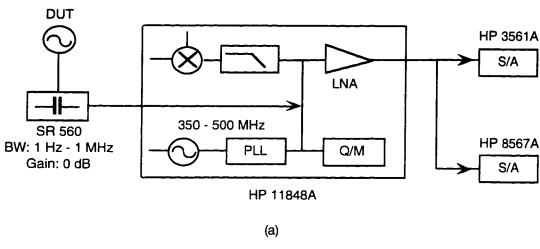

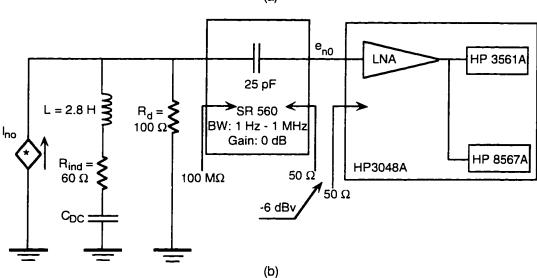

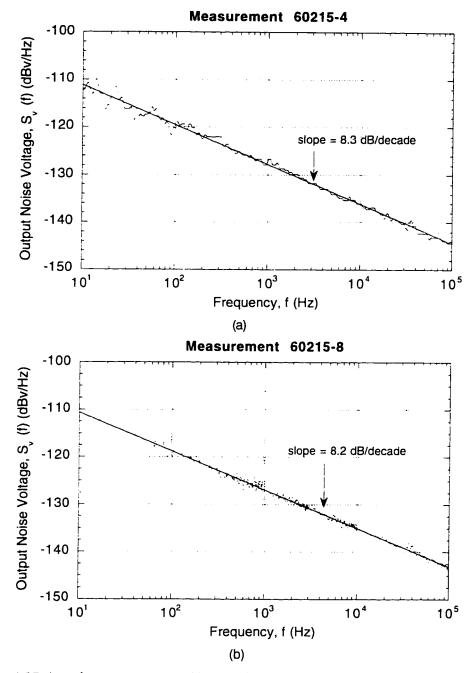

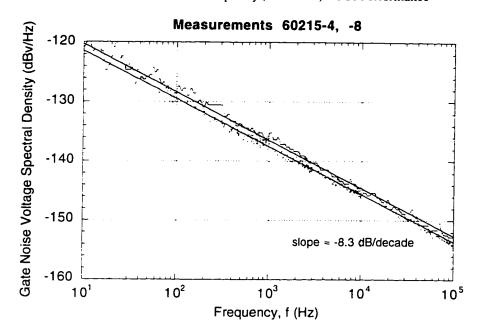

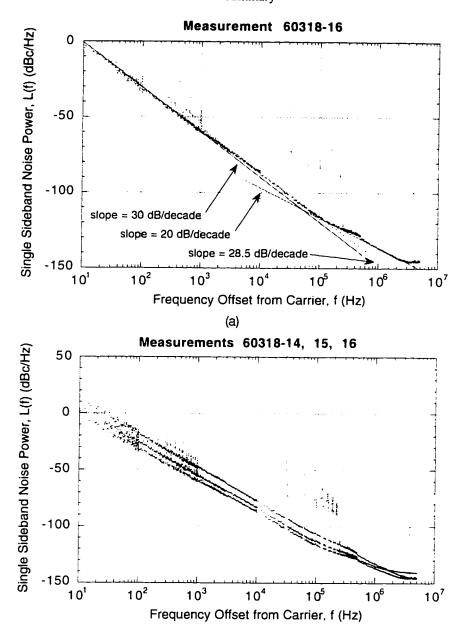

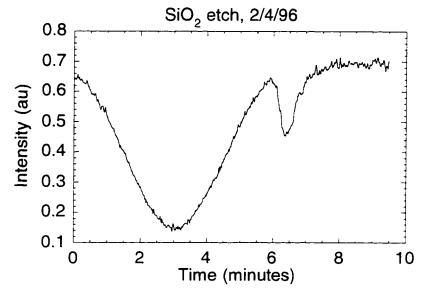

Figure 3.5.(d) Effects of annealing on the TLM resistances for regrowths on (a) regular, (b)  $\delta$ -doped, and (c) uniformly doped channel HEMTs.