### UNIVERSITY of CALIFORNIA Santa Barbara

# **Oxide Aperture Heterojunction Bipolar Transistors**

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

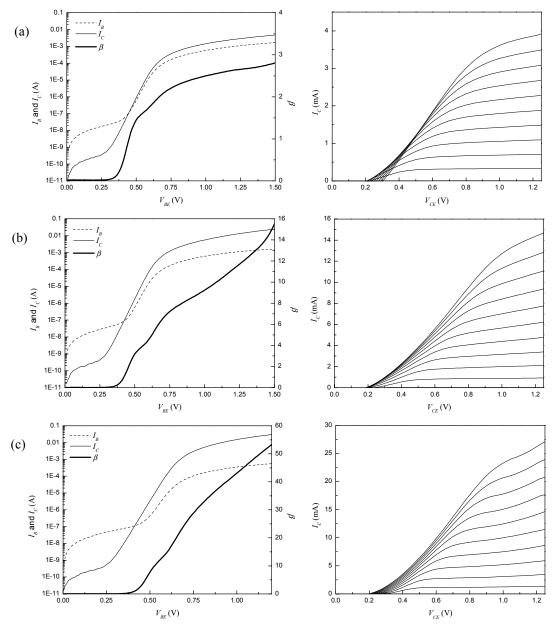

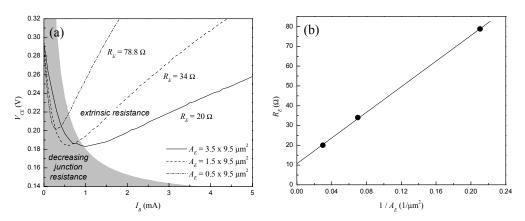

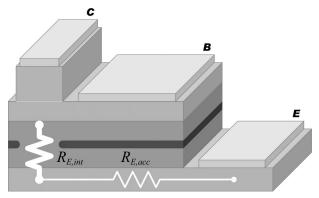

**Electrical and Computer Engineering**

by

James Galloway Champlain

Committee in charge:

Professor Umesh K. Mishra, Chair Professor Arthur C. Gossard Professor Evelyn L. Hu Professor James Speck

March 2002

The dissertation of James Galloway Champlain is approved.

Arthur C. Gossard

Evelyn L. Hu

James Speck

Umesh K. Mishra, Committee Chair

February 2002

Oxide Aperture Heterojunction Bipolar Transistors

Copyright © 2002 by James Galloway Champlain All right reserved

## Dedicated to

my parents, who taught me how to be a student of life,

and to

my sister Catherine, who taught me not to waste the gifts I was given

#### **Acknowledgments**

My time in graduate school at UCSB has been a true learning experience. The lessons that I have learned, both in and out of school, and the experiences I have collected will be with me always. I will always be indebted to Umesh Mishra for giving me the opportunity to be part of such an eclectic group of researchers, which granted me the benefit of being exposed to and part of a wide variety of research always on the cutting edge of technology, and for his guidance and support, which carried me through some of the more frustrating parts of my research. I'd also like to thank the remainder of my committee: Art Gossard who always gave a new and extraordinary view to the problem, Evelyn Hu whose insightful suggestions concerning oxidation and processing were of great benefit, and Jim Speck for his support and general interest in oxides and their applications.

Though most of my graduate career has been spent on projects alone, I'm thankful to the other members of the Mishra group (old and new) for their support and friendship: Ale, Ariel, Can, Dan, Dario, DJ, Gia, Haijiang, Huili, Ilan, Jae, Jason, Jeff, Lee, Likun, Mary, Naiqain, Nguyen, Peter, Prashant, Primit, Rama, Rob C., Rob U., Sten, Tim, Yifeng, and Yingda. I'd like to especially thank Yee Kwang, whose thought-provoking discussions concerning every aspect of bipolar transistors from growth to measurement and beautiful simulations of oxide aperture transistors have been invaluable. I'm grateful also to the York group, with whom I have shared the once spacious and now "cozy" Mishra-York office: Amit, Angelos, Baki, Bruce,

Chris, Hongtao, Jim, Joe, Justine, Nadia, Nick, Paolo, Pengcheng, Pete, Troy, and Vicki.

Many thanks go to John English. Working with him on the MBE system was like working with my father on one of our cars: lots of banging around and lots of swearing, but in the end it's fixed and you learned something along the way. Without John, nothing would have ever gotten done in the MBE lab. Thanks also go to the System B ("Da Bomb") growers, who have kept things interesting over the years. To the "old" guys, Eric, Prashant, Richard, and Sheila, thanks for all the help and fun; and to the "new" guys, Borys, Can, Dave, and Max, thanks for keeping the system running so I could finish my research.

Lastly, I'd like to thank all my friends and family. To Mom and Dad, I'll never be able to thank you for all the things you've given me. To my sisters, Jackie, Biz, and Catherine, having three older sisters was a learning experience in itself; thank you for being the remarkable and unique sisters that you are. Todd, Dave, and John, thanks for being the best buds in the world and for sticking by me through thick and thin. And thanks to all the friends I've met during my time here at UCSB: Nick, Omer, Cathy, Fay, Rex, Fereshteh, Neil, Peter, Lee, Rama, Heather, and especially Stefanie.

#### Vita

| December 29, 1972 | Born, Artesia, California, USA                                                                                                 |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------|

| May 1995          | Bachelor of Science in Electrical Engineering, Virginia<br>Polytechnic Institute and State University, Blacksburg,<br>Virginia |

| 1995-1996         | Teaching Assistant, University of California, Santa Barbara, California                                                        |

| 1996-2002         | Research Assistant, University of California, Santa Barbara, California                                                        |

| December 1996     | Masters of Science in Electrical and Computer Engineering,<br>University of California, Santa Barbara, California              |

| March 2002        | Doctor of Philosophy in Electrical and Computer Engineering,<br>University of California, Santa Barbara, California            |

#### **Publications**

- J. Champlain, C. Zheng, and U. Mishra, "LT (Al)GaAs and Al(Ga)As oxides for electronic applications." *Physik Mikrostrukturierter Halbleiter: 3<sup>rd</sup> Symposium on Non-Stoichiometric III-V Compounds (Special Edition)* **23**, 7-12 (2001)

- 2 A. Bek, A. Aydinli, J. G. Champlain, R. Naone, and N. Dagli, "A study of wet oxidized Al<sub>x</sub>Ga<sub>1-x</sub>As for integrated optics." *IEEE Photonics Technology Letters* **11**, 436-8 (1999)

- 3 E. Hall, A. R. Naone, J. E. English, H.-R. Blank, J. Champlain, and H. Kroemer, "Operational experience with a valved antimony cracker source for use in molecular beam epitaxy." *Journal of Vacuum Science & Technology B* **16**, 2660-4 (1998)

- 4 P. Chavarkar, J. Champlain, P. Parikh, and U. K. Mishra, "First demonstration of AlInAs/GaInAs HEMTs on AlAsSb and oxidized AlAsSb buffers." *Proc. of the International Conference on Indium Phosphide and Related Materials* Cape Cod, MA, 189-92 (1997)

- 5 U. K. Mishra, P. Parikh, P. Chavarkar, J. Yen, J. Champlain, B. Thibeault, H. Reese, S. S. Shi, E. Hu, L. Zhu, and J. Speck, "Oxide based compound

- semiconductor electronics." *International Electron Devices Meeting Technical Digest* Washington, DC, 545-8 (1997)

- 6 U. K. Mishra, P. Parikh, P. Chavarkar, and J. Champlain, "GaAs on Insulator (GOI) for low power applications." *Proc. of the Advanced Workshop on Frontiers in Electronics* Puerto de la Cruz, Spain 21-5 (1997)

#### Abstract

#### Oxide Aperture Heterojunction Bipolar Transistors

#### by James Galloway Champlain

The increasing demand in communication and radar technology for higher bit-rates and increased frequency resolution is eventually reflected in the requirement of devices being capable of operating at higher and higher frequencies. Currently, the greatest limitations on heterojunction bipolar transistor (HBT) speed are the extrinsic or parasitic components of the device, most notably the extrinsic base-collector capacitance. Various techniques and technologies have been employed to reduce the extrinsic base-collector capacitance in order to increase the frequency performance of the HBT: selective regrowth techniques, sidewall-contacted bases, undercut collectors, implanted emitters, and the transferred substrate technology. The oxide aperture HBT represents an alternative method to achieving a high frequency transistor.

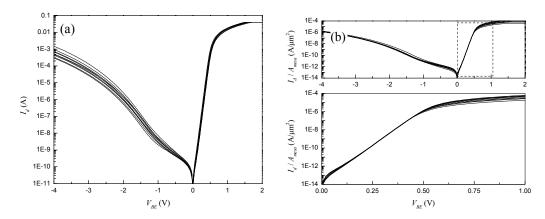

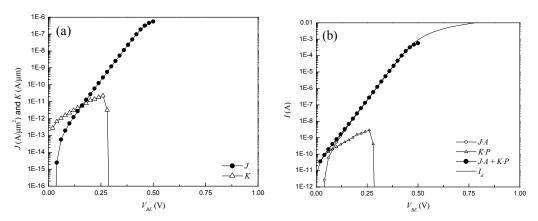

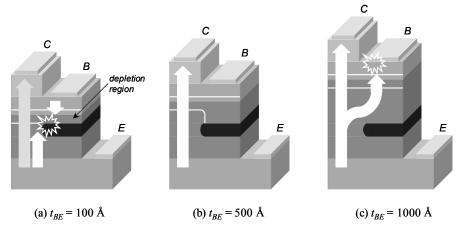

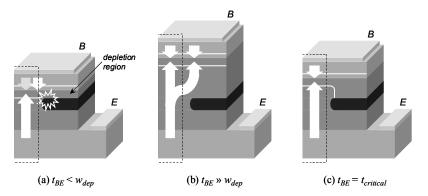

Concerns relating to the growth of arsenide-antimonide materials for transistor applications, the effect of an oxide on junction characteristics, and the high frequency performance of the oxide aperture HBT have been addressed. The placement of the oxide aperture, formed from the wet oxidation of  $AlAs_{0.56}Sb_{0.44}$ , was found to have a strong impact on the current-voltage characteristics of the base-emitter pn junction. Oxide apertures placed too close to the pn junction resulted in recombination

dominated characteristics; oxide apertures placed far from the *pn* junction resulted in poor channeling of the injected carriers, reducing the effectiveness of the aperture. Only oxide apertures placed within a critical range with respect to the *pn* junction, determined by material structure and doping, resulted in near ideal characteristics.

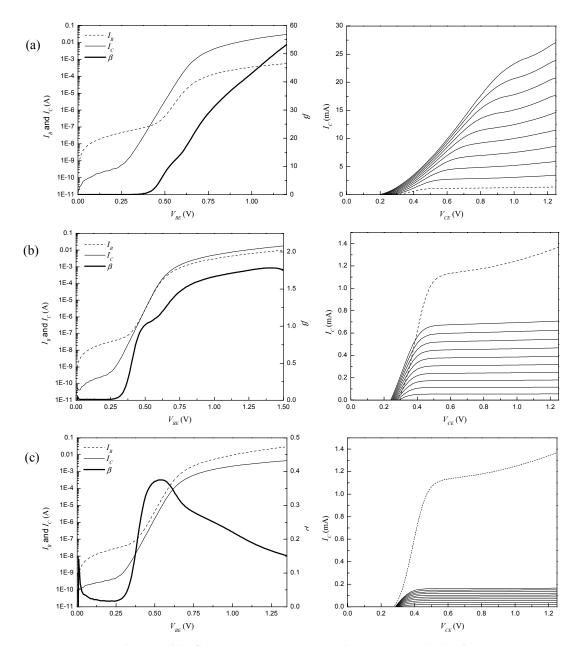

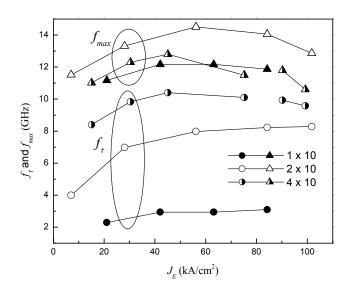

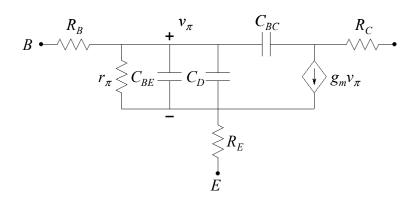

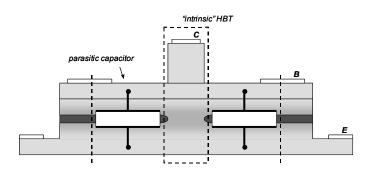

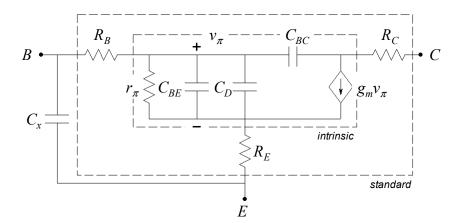

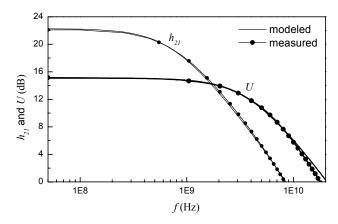

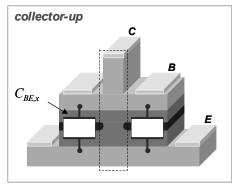

Investigation into the high frequency performance of the oxide aperture HBT showed that a parasitic base-emitter capacitance, inherent to the collector-up design adopted for the oxide aperture HBT, in conjunction with the relatively high emitter resistance of the oxide aperture HBT, due to the low mobility of electrons in the AlAs<sub>0.56</sub>Sb<sub>0.44</sub> emitter, resulted in an additional delay term in and thereby reduction of the current-gain cutoff frequency ( $f_t$ ). The added delay term was unexpectedly shown not to impact the maximum frequency of oscillation ( $f_{max}$ ). Oxide aperture HBTs with an  $f_t$  of 8 ~ 10 GHz and an  $f_{max}$  of 12 ~ 17 GHz, with a maximum measured  $f_{max}$  of 17.76 GHz, were demonstrated.

# **Table of Contents**

| Chapter 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                       |                                        |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| 1.1 Motivation for Oxide Aperture HBTs                                                                                                                                                                                                                                                                                                                                                                                       | 5                                      |  |

| Chapter 2 Oxides and Oxide Technology                                                                                                                                                                                                                                                                                                                                                                                        | 9                                      |  |

| <ul> <li>2.1 Introduction.</li> <li>2.2 The First Oxide: Silicon Dioxide.</li> <li>2.3 History of III-V Oxides.</li> <li>2.4 The First Oxide Aperture Devices: Laser Diodes.</li> <li>2.5 Oxide Aperture HBTs: High-Speed Devices?</li> <li>2.6 References.</li> </ul>                                                                                                                                                       | 9<br>11<br>17                          |  |

| Chapter 3 Transistor Design and Growth                                                                                                                                                                                                                                                                                                                                                                                       | 23                                     |  |

| 3.1 Introduction 3.2 Transistor Design: High Frequency Issues 3.3 Transistor Design: Material Selection 3.4 Growth of GaAs <sub>0.49</sub> Sb <sub>0.51</sub> and AlAs <sub>0.56</sub> Sb <sub>0.44</sub> 3.5 Growth of Al <sub>x</sub> Ga <sub>1-x</sub> As <sub>y</sub> Sb <sub>1-y</sub> Lattice-Matched to InP. 3.6 n-type Doping with Tellurium 3.7 Oxidation of AlAs <sub>0.56</sub> Sb <sub>0.44</sub> 3.8 References | 25<br>30<br>32<br>38<br>39<br>41<br>43 |  |

| Chapter 4 The Oxide Aperture Diode                                                                                                                                                                                                                                                                                                                                                                                           | 51                                     |  |

| <ul> <li>4.1 Introduction</li> <li>4.2 Diode Characteristics: Ideal versus Non-Ideal</li> <li>4.3 Design and Fabrication</li> <li>4.4 Diode Characteristics: Oxide Aperture Diodes</li> <li>4.5 Diode Design for Oxide Aperture HBTs</li> <li>4.6 References</li> </ul>                                                                                                                                                      |                                        |  |

| Chapter 5 The Oxide Aperture HBT                                                                                                                                                                                                                                                                                                                                                                                             | 75                                     |  |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                             | 75                                     |  |

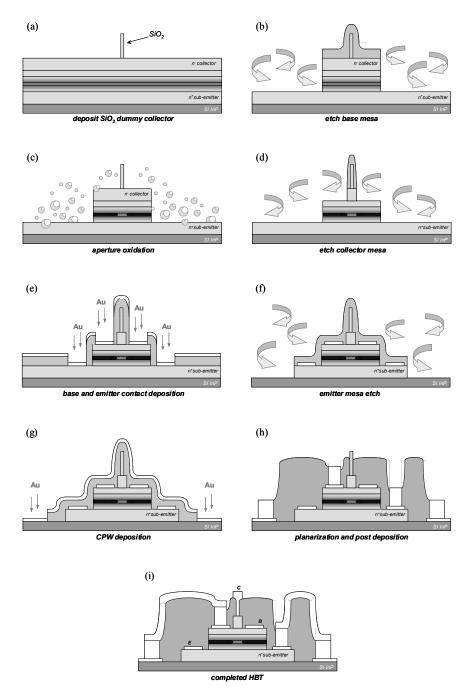

|    | 5.2 Oxide Aperture HBT Growth and Fabrication                             | 76        |

|----|---------------------------------------------------------------------------|-----------|

|    | 5.3 Oxide Aperture HBT: Generation Ø                                      |           |

|    | 5.4 Oxide Aperture HBT: Generation I                                      |           |

|    | 5.5 Oxide Aperture HBT: Generation II                                     |           |

|    | 5.6 Misaligned HBTs                                                       |           |

|    | 5.7 RF Measurements                                                       | 98        |

|    | 5.8 High-Frequency Device Model                                           | 105       |

|    | 5.9 References                                                            | 112       |

| Cł | hapter 6 Conclusions                                                      | 113       |

|    | 6.1 Oxide Apertures and pn Junctions                                      |           |

|    | 6.2 The Parasitic Base-Emitter Capacitance                                |           |

|    | 6.3 Future Work                                                           |           |

|    | 6.4 References                                                            | 123       |

| Αŗ | opendix A AIAs <sub>0.56</sub> Sb <sub>0.44</sub> Oxidation               | 125       |

| Αŗ | ppendix B Process and Fabrication Notes                                   | 131       |

|    | B.1 Oxide Aperture Diode Process                                          | 131       |

|    | B.2 Oxide Aperture Heterojunction Bipolar Transistor Process              |           |

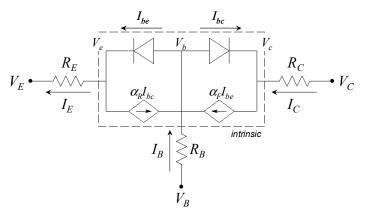

| Αŗ | ppendix C Ebers-Moll Bipolar Transistor Model                             | 147       |

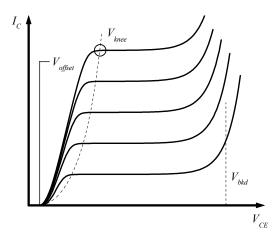

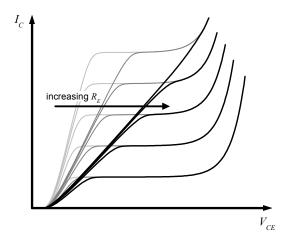

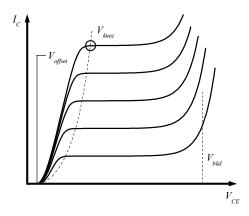

|    | C.1 The Offset Voltage                                                    | 149       |

|    | C.2 The Knee Voltage                                                      |           |

|    | C.3 References                                                            |           |

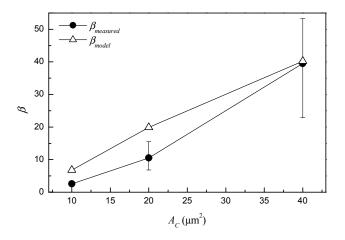

| Αŗ | opendix D Gain-Diffusion Model                                            | 153       |

|    | D.1 Gain-Diffusion Model                                                  | 154       |

|    | D.2 References                                                            |           |

| Αŗ | opendix E Derivation of $f_	au$ and $f_{max}$ with a Parasitic Input Capa | acitor161 |

|    | E.1 Derivation of $f_{\tau}$                                              | 164       |

|    | E.2 Derivation of $f_{max}$                                               | 173       |

|    | E.3 <i>Y</i> -parameters of an HBT with a Parasitic Capacitor             |           |

|    | E.4 References                                                            | 176       |

# CHAPTER 1

# Introduction

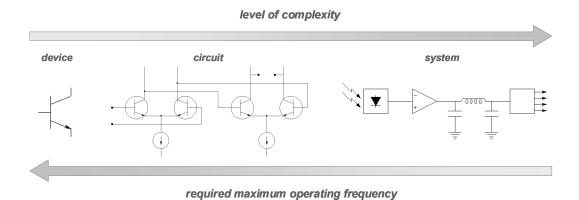

The ever-growing demand in communication and radar technology for increased bitrates and frequency resolution requires systems capable of providing increased bandwidth and clock rates.<sup>1,2</sup> This demand is eventually reflected in the requirement that the devices, which are the building blocks of these systems, must be capable of operating at higher and higher frequencies (Figure 1.1).<sup>3-6</sup>

For example, integrated circuits for optical fiber communications that are capable

Figure 1.1 Relationships between device, circuit, and systems.

of providing transmissions at 40 Gb/s are currently in development. The eventual emergence of higher bit-rate systems (i.e., 160 Gb/s) will require amplifiers with larger bandwidths (i.e., ~100 GHz). High bandwidth military radar and communication systems require analog-digital converters (ADCs), digital-analog converters (DACs), and direct-digital frequency synthesizers (DDFSs) with very high frequency resolution. This demands devices that can operate well over 100 times the signal bandwidth of the system.<sup>2</sup>

#### 1.1 Motivation for Oxide Aperture HBTs

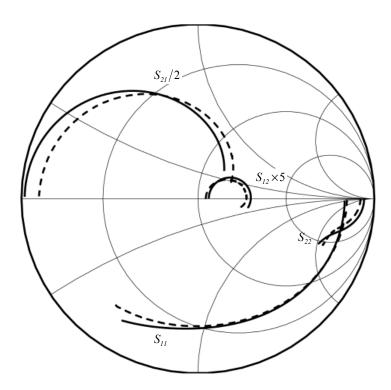

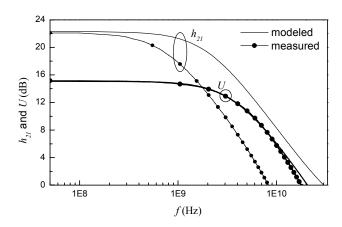

Two measures or figures-of-merit useful in evaluating the high frequency performance of a transistor are the current-gain cutoff frequency,  $f_{\tau}$ , and maximum frequency of oscillation,  $f_{max}$ .  $f_{\tau}$  is defined as the frequency at which the short-circuit current gain goes to unity.  $f_{max}$  is defined as the frequency at which the power gain goes to unity. Though finally dependent on the application, transistors with increased  $f_{\tau}$  and  $f_{max}$  must be realized in order to meet the demand in bandwidth of the next generation of systems.

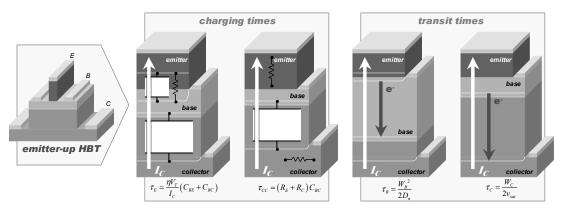

Roughly speaking,  $f_{\tau}$  corresponds to the transit time of carriers through the device. For a heterojunction bipolar transistor (HBT),  $f_{\tau}$  is written as:

$$f_{\tau} = \frac{1}{2\pi \left(\tau_{E} + \tau_{R} + \tau_{C} + \tau_{CC}\right)}$$

(1.1)

where  $\tau_E$  and  $\tau_{CC}$  are time constants related to the charging and discharging of the device and  $\tau_B$  and  $\tau_C$  are transit times through the device. In order to increase  $f_\tau$  in bipolar transistors, the relative time constants/transit times must be reduced. Without going into detail, this entails scaling the device vertically to decrease the distances across which the carriers transit. With the advent of precise growth techniques, like molecular beam epitaxy (MBE), which allow for the control of device layer thicknesses down to the atomic scale, vertical or epitaxial scaling is easily achieved, and transistors with  $f_\tau$  on the order of a few hundred gigahertz are possible.<sup>7,8</sup>

On the other hand,  $f_{max}$ , which is related to  $f_{\tau}$ , is strongly dependent upon the magnitude of the base resistance  $(R_B)$  and base-collector capacitance  $(C_{BC})$  time constant:

$$f_{max} = \sqrt{\frac{f_{\tau}}{8\pi R_B C_{BC}}} \tag{1.2}$$

$f_{max}$  is increased by reducing  $R_B$  and  $C_{BC}$  chiefly through increased doping in the base and horizontal or lithographic scaling. State-of-the-art conventional emitter-up

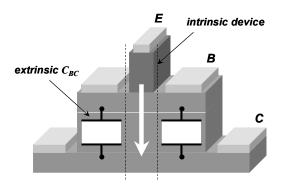

Figure 1.2 Illustration of the extrinsic base-collector capacitance present in a conventional emitter-up HBT.

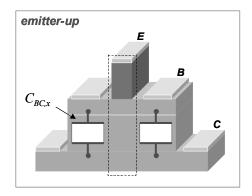

transistors with  $\sim 0.4 \,\mu\text{m}$  wide emitters demonstrate  $f_{max}$  of up to 300 GHz.<sup>8</sup> But commonly, conventional emitter-up transistors are still limited by the extrinsic base-collector capacitance underneath the base contacts (Figure 1.2). In contrast to the extrinsic (commonly referred to as "parasitic") base resistance that carries current between the base contacts and the intrinsic device, the extrinsic base-collector capacitance serves no purpose in the operation of the transistor and is truly "parasitic".

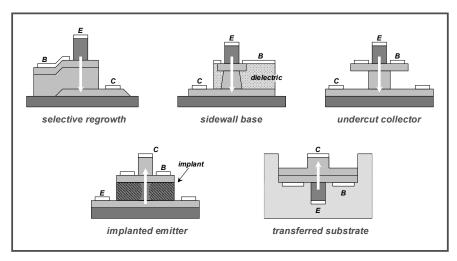

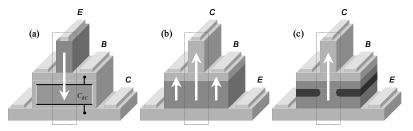

Various technologies and techniques that directly address the reduction of the extrinsic base-collector capacitance ( $C_{BC}$ ) with the purpose of increasing  $f_{max}$  have been examined: emitter-up transistors with regrown base-emitter junction, sidewall contacted bases, or undercut collectors; collector-up transistors with regrown base-collector junction or implanted extrinsic emitters; and the transferred substrate HBT (Figure 1.3). The oxide aperture HBT offers an alternative method to reducing  $C_{BC}$  while maintaining a high gain device.

Figure 1.3 Various methods used to reduce the base-collector capacitance of a HBT.

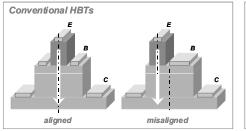

#### 1.2 The Oxide Aperture HBT

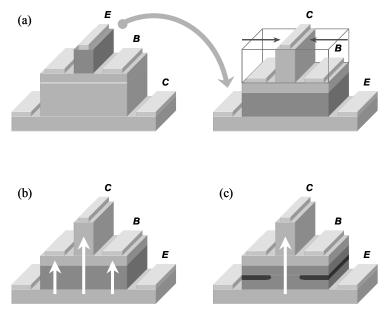

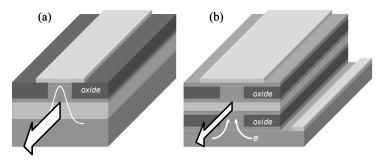

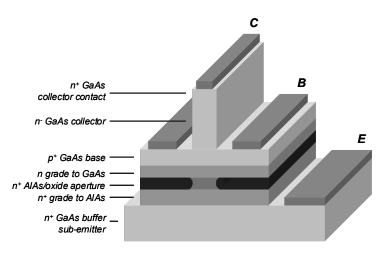

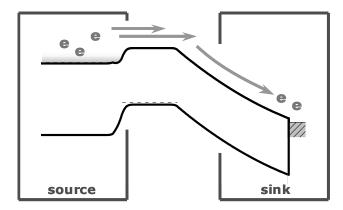

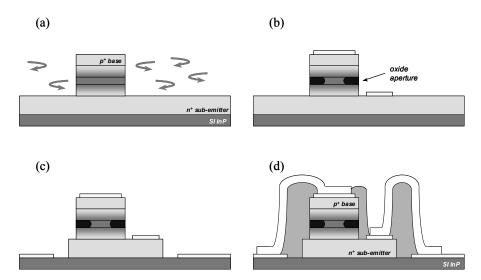

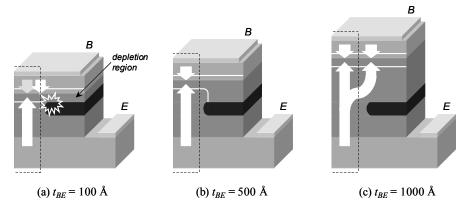

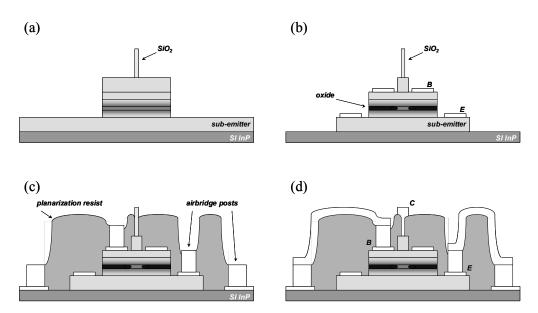

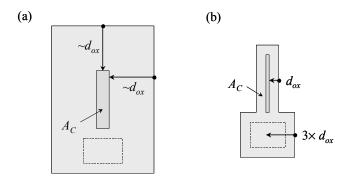

The oxide aperture HBT reduces the base-collector capacitance ( $C_{BC}$ ) simply by reducing the area of the base-collector junction (referred to as the collector area,  $A_C$ ). To reduce the collector area the device is "flipped" from the standard emitter-up into a collector-up configuration. This allows the collector area to be reduced through straightforward processing (Figure 1.4a).

Simply flipping the device is not sufficient to produce a high-quality transistor. If we were to stop here, we would be left with a transistor in which the collector area  $(A_C)$  is much smaller than the emitter area  $(A_E)$ . In such a device, the majority of the current injected into the base from the emitter would be collected at the base contacts

Figure 1.4 Illustration of the "development" of the oxide aperture HBT. (a) The emitter-up HBT is "flipped" and the collector area is reduced. (b) A simple collector-up device suffers from a greatly reduce current gain. (c) The oxide aperture HBT offers a device with a reduce base-collector capacitance while maintaining a high gain.

and not at the collector, resulting in a greatly reduced common-emitter current gain  $(\beta)$ , possibly reduced below  $\beta = 1$  (Figure 1.4b). In order to maintain a high gain device in a collector-up configuration, the current injected from the emitter must be channeled into the collector. In the oxide aperture HBT, this is achieved by means of an insulating oxide current aperture in the emitter. The end result is a collector-up transistor designed for high frequency operation by reducing  $C_{BC}$ , while maintaining the high-gain of an emitter-up transistor by means of an oxide current aperture (Figure 1.4c).

## 1.3 Synopsis of the Dissertation

This dissertation deals with the first work undertaken toward producing an RF compatible oxide aperture HBT. Chapter 2 presents a short history of oxides in semiconductors. The currently understood chemistry of the oxidation process as related to III-V semiconductors is presented, as well as various applications to optoelectronic and electronics devices. The chapter concludes with the only research to date on oxide aperture HBTs, begging the question, "What is the high frequency performance of these devices?"

Chapter 3 discusses the design and growth of the oxide aperture HBT. Issues regarding growth of transistors for high frequency operation, MBE growth of GaAs<sub>0.49</sub>Sb<sub>0.51</sub> and AlAs<sub>0.56</sub>Sb<sub>0.44</sub>, and the oxidation of AlAs<sub>0.56</sub>Sb<sub>0.44</sub> are examined. Concerns relating to achieving and maintaining lattice-matched compositions for

$GaAs_{0.49}Sb_{0.51}$ ,  $AlAs_{0.56}Sb_{0.44}$ , and  $Al_xGa_{1-x}As_ySb_{1-y}$  and the *n*-type doping of arsenide-anitmonides by tellurium, as opposed to silicon, are discussed.

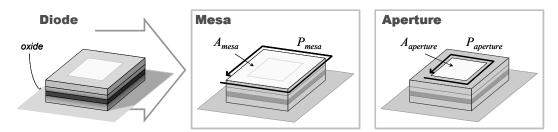

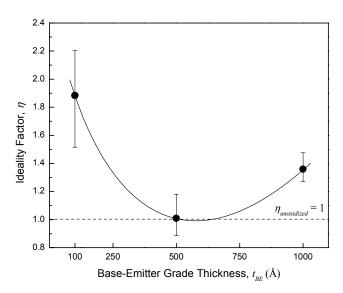

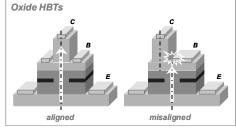

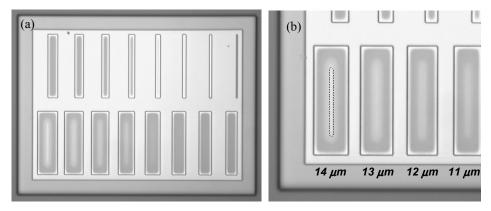

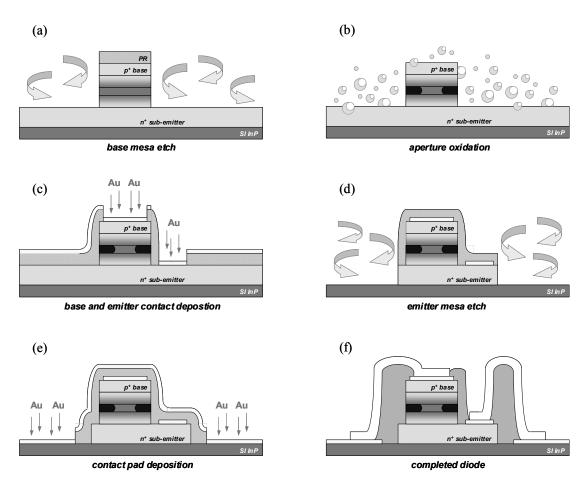

The design of the base-emitter junction as related to the oxide aperture HBT, referred to as the oxide aperture diode, is presented in Chapter 4. The effect of the "placement" of the oxide aperture within the device on the current-voltage characteristics of the diode is investigated. Current scaling with relation to diode and aperture size and the ideality of the conduction mechanism is examined. "Selection rules" or guidelines concerning the appropriate design of the base-emitter junction for the oxide aperture HBT are discussed.

In Chapter 5, work on the development of a high frequency oxide aperture HBT is examined. A final generation of transistors, designed and fabricated with improvements based on the results of previous generations, is analyzed. The high frequency performance of these devices is evaluated, and additional issues that arise as a result of the collector-up design and oxide aperture, such as a parasitic capacitance in the base-emitter junction, are discussed.

Conclusions and suggested future work concerning material selection, device design, and device processing are presented in Chapter 6.

#### 1.4 References

S. Mohammadi, J.-W. Park, D. Pavlidis, J.-L. Guyauz, and J. C. Garcia, "Design optimization and characterization of high-gain GaInP/GaAs HBT distributed amplifiers for high-bit-rate." *IEEE Transactions on Microwave Theory and Techniques* **48**, 1038-44 (2000).

- M. J. W. Rodwell, M. Urteaga, T. Mathew, D. Scott, D. Mensa, Q. Lee, J. Guthrie, Y. Bester, S. C. Martin, R. P. Smith, S. Jaganathan, S. Krishnan, S. I. Long, R. Pullela, B. Agarwal, U. Bhattacharya, L. Samoska, and M. Dahlstrom, "Submircon scaling of HBTs." *IEEE Transactions on Electron Devices* **48**, 2606-24 (2001).

- B. Agarwal, Q. Lee, R. Pullela, D. Mensa, J. Guthrie, and M. J. W. Rodwell, "A transferred-substrate HBT wide-band differential amplifier to 50 GHz." *IEEE Microwave and Guided Wave Letters* **8**, 263-5 (1998).

- M. Sokolich, A. R. Kramer, Y. K. Boegeman, and R. R. Martinez, "Demonstration of sub-5 ps CML ring oscillator gate delay with reduced parasitic AlInAs/InGaAs HBT." *IEEE Electron Device Letters* **22**, 309-11 (2001).

- T. Mathew, H.-J. Kim, D. Scott, S. Jaganathan, S. Krishnan, Y. Wei, M. Urteaga, S. Long, and M. J. W. Rodwell, "75 GHz ECL static frequency divider using InAlAs/InGaAs HBTs." *Electronics Letters* **37**, 667-8 (2001).

- T. Mathew, S. Jaganathan, D. Scott, S. Krishnan, Y. Wei, M. Urteaga, M. J. W. Rodwell, and S. Long, "2-bit adder: carry and sum logic circuits at 19 GHz clock frequency in InAlAs/InGaAs HBT technology." *Electronics Letters* **37**, 1156-7 (2001).

- M. Sokolich, C. H. Fields, and M. Madhav, "Submicron AlInAs/InGaAs HBT with 160 GHz  $f_T$  at 1 mA collector current." *IEEE Electron Device Letters* **22**, 8-10 (2001).

- M. W. Dvorak, C. R. Bolognesi, O. J. Pitts, and S. P. Watkins, "300 GHz InP/GaAsSb/InP Double HBTs with high current capability and BV<sub>CEO</sub> > 6 V." *IEEE Electron Device Letters* **22**, 361-3 (2001).

- Y.-F. Yang, C.-C. Hsu, E. S. Yang, and H.-J. Ou, "A High-Frequency GaInP/GaAs Heterjunction Bipolar Transistor with Reduced Base-Collector Capacitance Using a Selective Buried Sub-Collector." *IEEE Electron Device Letters* **17**, 531-3 (1996).

- K. Mochizuki, T. Tanoue, T. Oka, K. Ouchi, K. Hirata, and T. Nakamura, "High-speed InGap/GaAs transistors with sidewall base contact structure." *IEEE Electron Device Letters* **18**, 562-4 (1997).

- Y. Miyamoto, J. M. M. Rios, A. G. Dentai, and S. Chandrasekhar, "Reduction of base-collector capacitance by undercutting the collector and sub-collector in GaInAs/InP DHBT's." *IEEE Electron Device Letters* **17**, 97-9 (1996).

- H. C. Tseng and Y. Z. Ye, "High-performance, graded-base AlGaAs/InGaAs collector-up heterojunction bipolar transistors using a novel selective area regrowth process." *IEEE Electron Device Letters* **20**, 271-3 (1999).

- S. Yamahata, Y. Matsuoka, and T. Ishibashi, "High-f<sub>max</sub> collector-up AlGaAs/GaAs heterojunction bipolar transistors with a heavily carbon-doped base fabricated using oxygenion implantation." *IEEE Electron Device Letters* **14**, 173-5 (1993).

- Q. Lee, "Ultra-high bandwidth heterojunction bipolar transistors and millimeter-wave digital integrated circuits." *Ph. D. Thesis* Electrical and Computer Engineering Department, University of California, Santa Barbara 1999.

# CHAPTER 2

# **Oxides and Oxide Technology**

#### 2.1 Introduction

Given that this dissertation is not concerned with the specifics of the AlAs<sub>0.56</sub>Sb<sub>0.44</sub> wet oxidation reaction and the material aspects of the resultant oxide, other than its insulating nature, an overview of oxides and associated technologies was deemed fitting. Therefore, the following sections present a summary of oxides: their beginnings, applications, and some of the more salient issues related to the work presented in this dissertation.

#### 2.2 The First Oxide: Silicon Dioxide

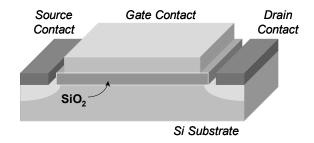

An oxide was employed as an integral element of an electronic device for the first time in 1960, when Kahng and Atalla proposed and fabricated the first metal-oxide-semiconductor field-effect transistor (MOSFET) using thermally oxidized silicon as the gate oxide (Figure 2.1).<sup>1</sup> The native oxide of silicon, silicon dioxide (SiO<sub>2</sub>), has

since been employed in innumerable fashions in the silicon electronics industry, from

Figure 2.1 Illustration of a Si MOSFET.

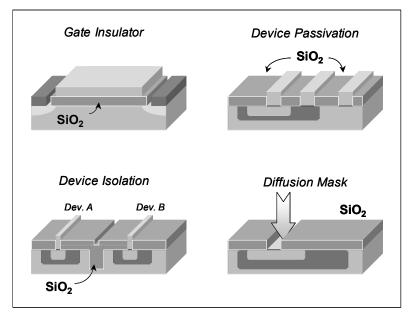

gate insulators to device passivation, from device isolation to doping diffusion masks (Figure 2.2). The means by which silicon dioxide has been produced are as widely varied.<sup>2,3</sup> The result is an integrated circuit technology that has generated multibillion-dollar markets.

Figure 2.2 Various applications for silicon dioxide (SiO<sub>2</sub>)

Similar techniques have been attempted with GaAs to achieve a native oxide with similar properties to SiO<sub>2</sub> (e.g., high density, low interface state density, mechanically

stable, insulating),<sup>2</sup> but the results have been disappointing.<sup>3-5</sup> Not until the past decade has any progress been made into developing oxides for III-V semiconductor materials.<sup>4-21</sup>

### 2.3 History of III-V Oxides

Most of the initial work on III-V oxides was centered on the native oxides of GaAs.<sup>3,22</sup> The resultant oxide films invariably consisted of a nonstoichiometric combination of gallium oxide (Ga<sub>2</sub>O<sub>3</sub>), arsenic oxide (As<sub>2</sub>O<sub>3</sub>), and arsenic, and tended to be mechanically and chemically unstable, in addition to being poor electrical insulators.<sup>3-5</sup> Deposited oxides or dielectrics have proved to be useful as passivation films, diffusion masks, or simply as physical protection for III-V semiconductors, but due to their usually high interface state densities, deposited oxides have shown to be useless for electronic applications.<sup>23,24</sup> It wasn't until the work of Dallesasse *et al.*<sup>5,6</sup> that the hope of having a stable oxide for use in the III-V materials system was renewed.

Though the first reported work on the wet oxidation of Al<sub>x</sub>Ga<sub>1-x</sub>As compounds was in 1979, when a native oxide of AlAs was formed at a very low oxidation temperature of 100 °C,<sup>25</sup> it wasn't until 1990 when Dallesasse discovered that the wet oxidation of AlAs at temperatures above ~300 °C resulted in a mechanically robust form of the native oxide of AlAs.<sup>5</sup> Since that time much work and research has gone into the wet oxidation of Al<sub>x</sub>Ga<sub>1-x</sub>As and its resultant oxide, Al<sub>2</sub>O<sub>3</sub>.<sup>6-18,26-29</sup> Applications for the oxide have been found in all aspects of electronics and opto-

electronics; ranging from gate insulators<sup>19,30</sup> to insulating backgates and buffers,<sup>10,17</sup> from low index waveguides and current apertures<sup>15,29,31</sup> to mirrors and lenses.<sup>9,13,20</sup>

Ashby *et al.* have proposed the following chemical reactions for the formation of Al<sub>2</sub>O<sub>3</sub> from AlAs by wet oxidation:<sup>32</sup>

2 AlAs + 6 H<sub>2</sub>O(g)

$$\rightarrow$$

Al<sub>2</sub>O<sub>3</sub> + As<sub>2</sub>O<sub>3</sub>(l) + 6 H<sub>2</sub>

$$\Delta G^{698} = -473 \text{ kJ/mol}$$

(2.1)

$$As_2O_3(l) + 3 H_2 \rightarrow 2 As + 3 H_2O(g)$$

$\Delta G^{698} = -131 \text{ kJ/mol}$  (2.2)

$$As_2O_3(l) + 6 H \rightarrow 2 As + 3 H_2O(g)$$

$\Delta G^{698} = -1226 \text{ kJ/mol}$  (2.3)

It should be noted that the values presented here for the Gibb's free energy,  $\Delta G$ , are for reactions carried out at a temperature of 400 °C (698 K). The negative values for  $\Delta G$  indicate that these reactions are spontaneous at the given temperature; in other words, they will occur without additional energy being introduced into the system.

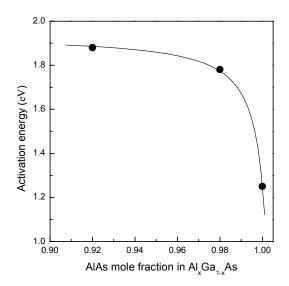

Replacing AlAs with GaAs in Equation (2.1) results in a  $\Delta G^{698} = +10$  kJ/mol for that reaction.<sup>4</sup> This suggests that exchanging Al for Ga, as in Al<sub>x</sub>Ga<sub>1-x</sub>As, would make the reaction in Equation (2.1) less favorable, retarding the wet oxidation reaction as the Ga content increases (Figure 2.3). Work by Choquette *et al.*,<sup>4</sup> as well as others, <sup>13,15,29</sup> supports this proposal (Figure 2.4).

In addition to the composition of the oxidizing layer, Naone *et al.* found that the wet oxidation reaction of Al<sub>x</sub>Ga<sub>1-x</sub>As was dependent upon the thickness of the

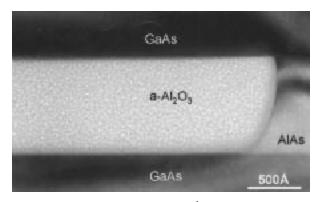

Figure 2.3 From Choquette et al.. Cross-sectional TEM image of an oxidized layer converted from a 100 nm thick AlAs layer surrounded by layers of GaAs demonstrating the selective oxidation of AlAs over GaAs.

Figure 2.4 After Choquette  $\it et al..^4$  Arrhenius activation energy for the oxidation reaction of  $Al_xGa_{1-x}As$  versus Al composition.

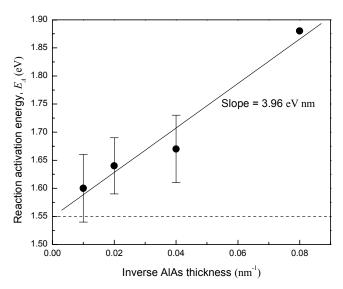

oxidizing layer. In short, it was proposed that the interfacial energies between the relevant materials (i.e., GaAs, AlAs, and Al<sub>2</sub>O<sub>3</sub>) produced a "drag" on the oxidation front. As a result of the balancing of these energies, this drag increased as the AlAs

layer thickness decreased, increasing the activation energy of the reaction and reducing the oxidation rate (Figure 2.5). It was also proposed that varying the composition of the layers cladding the oxidation layer would modify the oxidation reaction, due to an alteration to the interfacial energy balance.<sup>16</sup> Further work by Naone *et al.*, <sup>15,29</sup> as well as others, <sup>9,13</sup> supports this statement.

Figure 2.5 After Naone *et al.*. <sup>16</sup> The activation energies of the linear rate coefficient,  $k_b$  as a function of 1/thickness.

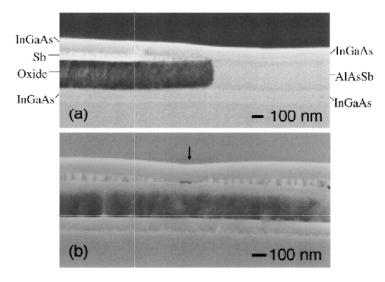

In contrast to the work seen with the oxidation of Al<sub>x</sub>Ga<sub>1-x</sub>As, the oxide formed from the wet oxidation of AlAs<sub>0.56</sub>Sb<sub>0.44</sub> has seen little use.<sup>33,34</sup> This is primarily due to the formation of a thin "float layer" of antimony metal (a mixture of amorphous and crystalline antimony) at the interface between the oxide and semiconductor during oxidation (Figure 2.6).<sup>35,36</sup> This metallic antimony layer tends to be highly conductive, generally resulting in electrical shorts in devices that partially or completely degrade the electronic performance of devices.<sup>33</sup> Nonetheless, in at least

one case these antimony layers have been used in a beneficial manner to reduce the extrinsic base resistance seen in a collector-up HBT.<sup>34</sup>

Figure 2.6 From Blum et al..<sup>35</sup> Cross-sectional scanning electron micrograph of oxidized InGaAs/AlAsSb/InGaAs structure. (a) partially oxidized layer and (b) fully oxidized layer.

The most extensive study done on the wet oxidation of  $AlAs_{0.56}Sb_{0.44}$  to date was by Mathis *et al.*.<sup>36</sup> The lateral oxidation kinetics of  $AlAs_{0.56}Sb_{0.44}$  and  $Al_xGa_{1-x}As_ySb_{1-y}$  (lattice-matched to InP) were found to be similar to  $Al_xGa_{1-x}As$  in terms of temperature, thickness, and composition dependence, with a few noteworthy exceptions.

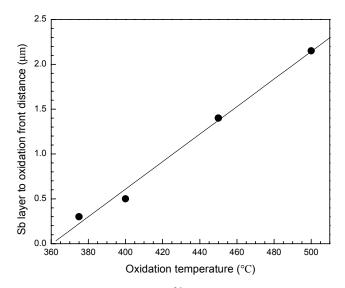

In addition to the formation of an antimony float layer, it was found that this float layer lagged behind the oxidation front, and that the amount of lag increased with increasing oxidation temperature (Figure 2.7). At temperatures higher than 450 °C, AlAs<sub>0.56</sub>Sb<sub>0.44</sub> experiences self-limiting oxidation and the apparent diffusion constant approaches zero. It was proposed that this self-limiting oxidation is a result of a

physical change of the reaction layer at the oxidation front that is due to an increased solubility of antimony in  $Al_2O_3$ . At higher temperatures antimony may be increasingly incorporated into the oxidation layer, given that the antimony mobility is small compared to the rate of mass transport through the reaction layer. The result of this can be seen in the increasing lag distance for the antimony float layer at higher

Figure 2.7 After Mathis *et al.*.<sup>36</sup> Distance from oxidation front to antimony segregation layer, measured by cross-sectional SEM, as a function of oxidation temperature after oxidation for 30 min. The antimony segregation layer lags the oxidation front for each sample, and increases to a maximum measured distance of 2.2  $\mu$ m at 500 °C.

temperatures (Figure 2.7). Increased incorporation of oxidized antimony into the reaction layer prevents further diffusion of reactants, resulting in the oxidation slowing until lateral oxidation is no longer measurable.<sup>36</sup>

### 2.4 The First Oxide Aperture Devices: Laser Diodes

The first devices that used the native oxide formed from the wet oxidation of Al<sub>x</sub>Ga<sub>1-x</sub>As were planar edge-emitting laser diodes,<sup>37,38</sup> where the oxide layers were used for index guiding<sup>39</sup> and as current apertures (Figure 2.8).<sup>40</sup>

Figure 2.8 (a) Example of a planar laser diode with oxide for index guiding. (b) Example of a planar laser diode with oxide as a current aperture.

Vertical-cavity surface-emitting lasers (VCSELs) that incorporate buried oxide apertures for electrical and optical confinement have shown dramatic increases in performance. VCSELs have used oxide apertures underneath dielectric distributed Bragg reflectors, significantly reducing their threshold current.<sup>41</sup> Monolithic VCSELs have exploited the oxidation selectivity of the low refractive index Al<sub>x</sub>Ga<sub>1-x</sub>As layers within a semiconductor distributed Bragg reflector to form one or more oxide apertures.<sup>42,43</sup> VCSELs of this form have demonstrated the lowest threshold current<sup>44</sup> and voltage,<sup>42</sup> in addition to record high power conversion efficiencies.<sup>45</sup> Moreover, the relative refractive index of the oxidized regions is ~1.6, reduced from that of the original Al<sub>x</sub>Ga<sub>1-x</sub>As (~3.0),<sup>39</sup> resulting in index guiding optical confinement, evident by the emission characteristics<sup>46</sup> and reduced threshold

currents.  $^{41,44}$  The low index oxide has also been utilized in high index contrast mirrors consisting of GaAs-Al<sub>2</sub>O<sub>3</sub> layers.  $^{47}$

### 2.5 Oxide Aperture HBTs: High-Speed Devices?

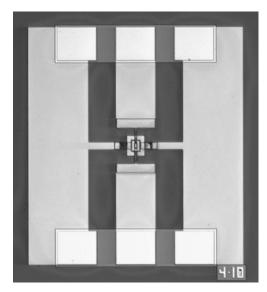

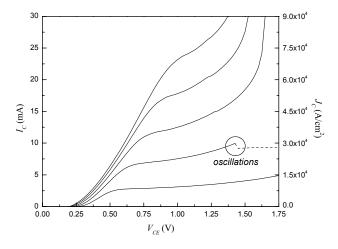

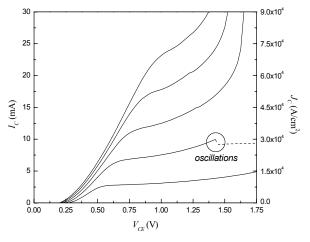

To date, only two groups have produced HBTs using a native oxide as a current aperture. The first was Massengale *et al.*, who fabricated an Npn collector-up  $Al_xGa_{1-x}As/GaAs$  HBT using oxidized AlAs as a current aperture in the emitter (Figure 2.9). Devices displayed current gains on the order of 35~50, with current densities up to  $10^5$  A/cm<sup>2</sup>.<sup>12</sup>

Figure 2.9 Illustration of the collector-up AlGaAs/GaAs HBT presented by Massengale *et al.*. 12

The only other work with HBTs having a native oxide current aperture was by Lear *et al.*. A Pnp collector-up HBT in the InP lattice-matched material system was fabricated using the native oxide of  $AlAs_{0.56}Sb_{0.44}$  as the current aperture in the emitter. The result was devices with current gains of approximately  $20\sim30$  at current densities of  $10^4$  A/cm<sup>2</sup>. A reduced extrinsic base resistance was also observed, due to

the formation during oxidation of a highly conductive float layer of antimony directly below the base.<sup>34</sup>

In both cases, the claimed motivation behind fabricating such a device is the reduction of the base-collector capacitance commonly associated with mesa structure HBTs,<sup>34</sup> with the ultimate goal of improved frequency performance.<sup>12,48</sup> But in neither case were anything but DC results reported, leaving the high-speed performance of such devices in question.

#### 2.6 References

- D. Kahng, "A historical perspective on the development of MOS transistors and related devices." *IEEE Transactions on Electron Devices* **ED-23**, 655-7 (1976).

- L. E. Katz, "Oxidation" in *VLSI technology*, second ed., edited by S. M. Sze (McGraw-Hill, Inc., New York, 1988), pp. 98-140.

- S. K. Ghandhi, "Native films" in *VLSI fabrication principles: silicon and gallium arsenide*, second ed., edited by S. K. Ghandhi (John Wiley & Sons, Inc., New York, 1994), pp. 451-509.

- K. D. Choquette, K. M. Geib, C. I. H. Ashby, R. D. Twesten, O. Blum, H. Q. Hou, D. M. Follstaedt, E. Hammons, D. Mathes, and R. Hull, "Advances in selective wet oxidation of AlGaAs alloys." *IEEE Journal of Selected Topics in Quantum Electronics* 3, 916-26 (1997).

- J. M. Dallesasse, N. El-Zein, N. Holonyak, Jr., K. C. Hsieh, R. D. Burnham, and R. D. Dupuis, "Environmental degradation of Al<sub>x</sub>Ga<sub>1-x</sub>As-GaAs quantum-well heterostructures." *Journal of Applied Physics* 68, 2235-8 (1990).

- J. M. Dallesasse, N. Holonyak, Jr., A. R. Sugg, T. A. Richard, and N. El-Zein, "Hydrolyzation oxidation of Al<sub>x</sub>Ga<sub>1-x</sub>As-AlAs-GaAs quantum well heterostructures and superlattices." *Applied Physics Letters* **57**, 2844-6 (1991).

- A. R. Sugg, E. I. Chen, T. A. Richard, N. Holonyak, Jr., and K. C. Hsieh, "Native oxide-embedded Al<sub>y</sub>Ga<sub>1-y</sub>As-GaAs-In<sub>x</sub>Ga<sub>1-x</sub>As quantum well heterostructure lasers." *Applied Physics Letters* **62**, 1259-61 (1993).

- J. A. Kash, B. Pezeshki, F. Agahi, and N. A. Bojarczuk, "Recombination in GaAs at the AlAs oxide-GaAs interface." *Applied Physics Letters* **67**, 2022-4 (1995).

- O. Blum, K. L. Lear, H. Q. Hou, and M. E. Warren, "Buried refractive mircolenses formed by selective oxidation of AlGaAs." *Electronics Letters* **32**, 1406-8 (1996).

- A. E. Bond, Chao-Kun Lin, M. H. MacDougal, P. D. Dapkus, K. Kaviani, O. Adamczyk, and R. Nottenburg, "Backgating reduction in MESFET's using an AlAs native oxide buffer layer." *Electronics Letters* **32**, 2271-3 (1996).

- J. A. Kash, S. Guha, B. Pezeshki, F. Agahi, and N. A. Bojarczuk, "Electronic and structural properties of the selectively wet-oxidized AlAs-GaAs interface." *CLEO '96: Conference on Lasers and Electro-Optics 1996* Anaheim, CA, USA, 473 (1996).

- A. Massengale, M. C. Larson, C. Dai, and J. S. Harris, Jr., "Collector-up AlGaAs/GaAs heterojunction bipolar transistors using oxidised AlAs for current confinement." *Electronics Letters* **32**, 399-401 (1996).

- O. Blum, C. I. H. Ashby, and H. Q. Hou, "Barrier-layer-thickness control of selective wet oxidation of AlGaAs for embedded optical elements." *Applied Physics Letters* **70**, 2870-2 (1997).

- H. Gebretsakik, K. Zhang, K. Kamath, X. Zhang, and P. Bhattacharya, "Recombination characteristics of minority carriers near the Al<sub>x</sub>O<sub>y</sub>/GaAs interface using the light beam induced current technique." *Applied Physics Letters* **71**, 3865-7 (1997).

- R. L. Naone, E. R. Hegblom, B. J. Thibeault, and L. A. Coldren, "Oxidation of AlGaAs layers for tapered apertures in vertical-cavity." *Electronics Letters* **33**, 300-1 (1997).

- R. L. Naone and L. A. Coldren, "Surface energy model for the thickness dependence of the lateral oxidation of AlAs." *Journal of Applied Physics* **82**, 2277-80 (1997).

- P. Parikh, P. M. Chavarkar, and U. K. Mishra, "GaAs MESFET's on a truly insulating buffer layer: demonstration of the GaAs on insulator technology." *IEEE Electron Device Letters* **18**, 111-13 (1997).

- S. A. Feld, J. P. Loehr, R. E. Sherriff, J. Wiemeri, and R. Kaspi, "In situ optical monitoring of AlAs wet oxidation using a novel low-temperature low-pressure steam furnace design." *IEEE Photonics Technology Letters* **10**, 197-9 (1998).

- C. B. DeMelo, D. C. Hall, G. L. Snider, D. Xu, G. Kramer, and N. El-Zein, "High electron mobility InGaAs-GaAs field effect transistor with thermally oxidised AlAs gate insulator." *Electronics Letters* 36, 84-6 (2000).

- D. A. Kellogg, N. Holonyak, Jr., and R. D. Dupuis, "Reliability of photopumped Al<sub>x</sub>Ga<sub>1-x</sub>As-GaAs quantum well heterostructure lasers with top and bottom distributed native-oxide reflectors." *Applied Physics Letters* **77**, 1608-10 (2000).

- G. W. Pickrell, J. H. Epple, K. L. Chang, K. C. Hsieh, and K. Y. Cheng, "Improvement of wet-oxidized Al<sub>x</sub>Ga<sub>1-x</sub>As (x~1) through the use of AlAs/GaAs digital alloys." *Applied Physics Letters* **76**, 2544-6 (2000).

- C. W. Wilmsen, "Oxide/III-V compound semiconductor interfaces" in *Physics and chemistry of III-V compound semiconductor interfaces*, edited by C. W. Wilmsen (Plenum, New York, 1985), pp. 402-62.

- A. C. Adams, "Dielectric and polysilicon film deposition" in *VLSI technology*, second ed., edited by S. M. Sze (McGraw-Hill, Inc., New York, 1988), pp. 233-71.

- S. K. Ghandhi, "Deposited films" in *VLSI fabrication principles: silicon and gallium arsenide*, second ed., edited by S. K. Ghandhi (John Wiley & Sons, Inc., New York, 1994), pp. 510-86.

- T. W. Tsang, "Self-terminating thermal oxidation of AlAs epilayers grown on GaAs by molecular beam epitaxy." *Applied Physics Letters* **57**, 426-9 (1978).

- J. A. Kash, B. Pezeshki, F. Agahi, and N. A. Bojarczuk, "Interface recombination at the selectively wet-oxidized AlAs-GaAs interface." *IEEE LEOS '95: Lasers and Electro-Optics Society 1995 Annual Meeting San Francisco*, CA, USA, 83-4 vol.1 (1995).

- S. A. Feld, J. P. Loehr, R. E. Sherriff, J. Wiemeri, and R. Kaspi, "Kinetics of AlAs steam oxidation at low pressure and low temperature measured in-situ using a novel furnace design with an integral optical port." *IEEE Twenty-Fourth International Symposium on Compound Semiconductors Compound* San Diego, CA, USA, 325-8 (1998).

- J. P. Loehr and S. A. Feld, "Control and stability of AlAs wet oxidation studied by in-situ optical monitoring in a low-pressure, low-temperature steam furnace." *IEEE LEOS'98: Lasers and Electro-Optics Society 1998 Annual Meeting* Orlando, FL, USA, 110-11 vol.2 (1998).

- <sup>29</sup> R. L. Naone and L. A. Coldren, "Tapered air apertures for thermally robust VCL structures." *IEEE Photonics Technology Letters* **11**, 1339-41 (1999).

- B.-K. Jun, D.-H. Kim, J.-Y. Leem, J.-H. Lee, and Y.-H. Lee, "Fabrication of a depletion mode GaAs MOSFET using Al<sub>2</sub>O<sub>3</sub> as a gate insulator through the selective wet oxidation of AlAs." *Thin Solid Films* **360**, 229-32 (2000).

- H.-H. Kim, D.-C. e. Oh, S.-L. Hwang, Y.-D. Bae, K.-H. Sung, and J.-J. Jung, "High performance AlAs native oxide-confined GaInP/AlGaInP 635 nm laser diode." *IEEE LEOS '98: Lasers and Electro-Optics Society 1998 Annual Meeting* Orlando, FL, USA, **2:** 181-2 (1998).

- C. I. H. Ashby, J. P. Sullivan, K. D. Choquette, K. M. Geib, and H. Q. Hou, "Wet oxidation of AlGaAs: the role of hydrogen." *Journal of Applied Physics* **82**, 3134-6 (1997).

- P. Chavarkar, J. Champlain, P. Parikh, and U. K. Mishra, "First demonstration of AllnAs/InGaAs HEMTs on AlAsSb and oxidized AlAsSb buffers." *Ninth International Conference on Indium Phosphide and Related Materials* Cape Cod, MA, USA, 189-92 (1997).

- K. L. Lear, O. Blum, and J. F. Klem, "Oxide defined AlAsSb/InGaAs/InP heterojunction bipolar transistors with a buried metal extrinsic base." 55th Annual Device Research Conference Fort Collins, CO, USA, 66-7 (1997).

- O. Blum, K. M. Geib, M. J. Hafich, J. F. Klem, and C. I. H. Ashby, "Wet thermal oxidation of AlAsSb lattice matched to InP for optoelectronic applications." *Applied Physics Letters* **68**, 3129-31 (1996).

- S. K. Mathis, K. H. A. Lau, A. M. Andrews, E. M. Hall, G. Almuneau, E. L. Hu, and J. S. Speck, "Lateral oxidation kinetics of AlAsSb and related alloys lattice matched to InP." *Journal of Applied Physics* **89**, 2458-64 (2001).

- J. M. Dallesasse and N. Holonyak, Jr., "Native-oxide stripe-geometry Al<sub>x</sub>Ga<sub>1-x</sub>As-GaAs quantum well heterostructure lasers." *Applied Physics Letters* **58**, 394-6 (1991).

- S. A. Maranowski, F. A. Kish, S. J. Caracci, N. Holonyak, Jr., J. M. Dallesasse, D. P. Bour, and D. W. Treat, "Native-oxide defined In<sub>0.5</sub>(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>0.5</sub>P quantum well heterostructure window lasers (660 nm)." *Applied Physics Letters* **61**, 1688-90 (1992).

- F. A. Kish, S. J. Caracci, N. Holonyak, Jr., J. M. Dallesasse, K. C. Hsieh, M. J. Ries, S. C. Smith, and R. D. Burnham, "Planar native-oxide index-guide Al<sub>x</sub>Ga<sub>1-x</sub>As-GaAs quantum well heterostructure lasers." *Applied Physics Letters* **59**, 1755-7 (1991).

- S. A. Maranowski, A. R. Sugg, E. I. Chen, and N. Holonyak, Jr., "Native oxide top-and bottom-confined narrow stripe p-n Al<sub>y</sub>Ga<sub>1-y</sub>As-GaAs-In<sub>x</sub>Ga<sub>1-x</sub>As quantum well heterostructure laser." *Applied Physics Letters* **63**, 1660-2 (1993).

- D. L. Huffaker, D. G. Deppe, K. Kumar, and T. J. Rogers, "Native-oxide defined ring contact for low threshold vertical-cavity lasers." *Applied Physics Letters* **65**, 97-9 (1994).

- K. D. Choquette, R. P. Schneider, Jr., K. L. Lear, and K. M. Geib, "Low threshold voltage vertical-cavity lasers fabricated by selective oxidation." *Electronics Letters* **30**, 2043-4 (1994).

- K. D. Choquette, K. L. Lear, R. P. Schneider, Jr., K. M. Geib, J. J. Figiel, and R. Hull, "Fabrication and performance of selectively oxidized vertical-cavity lasers." *IEEE Photonics Technology Letters* 7, 1237-9 (1995).

- G. M. Yang, M. H. MacDougal, and P. D. Dapkus, "Ultralow threshold current vertical-cavity surface-emitting lasers obtained with selective oxidation." *Electronics Letters* **31**, 886-8 (1995).

- K. L. Lear, K. D. Choquette, R. P. Schneider, Jr., S. P. Kilcoyne, and K. M. Geib, "Selectively oxdised vertical cavity surface emitting lasers with 50% power conversion efficiency." *Electronics Letters* 31, 208-9 (1995).

- K. L. Lear, K. D. Choquette, R. P. Schneider, Jr., and S. P. Kilcoyne, "Modal analysis of a small surface emitting laser with a selectively oxidized waveguide." *Applied Physics Letters* 66, 2616-18 (1995).

- M. H. MacDougal, P. D. Dapkus, V. Pudikov, Hanmin Zhao, and G. M. Yang, "Ultralow threshold current vertical-cavity surface-emitting lasers with AlAs oxide-GaAs distributed Bragg reflectors." *IEEE Photonics Technology Letters* 7, 229-31 (1995).

- <sup>48</sup> H. Kroemer, "Heterostructure bipolar transistors and integrated circuits." *Proceedings of the IEEE* **70**, 13-25 (1982).

# CHAPTER 3

# **Transistor Design and Growth**

#### 3.1 Introduction

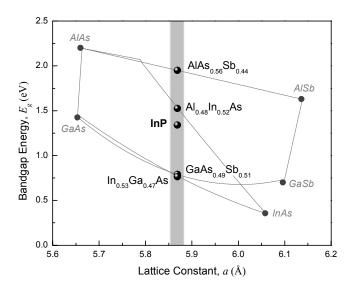

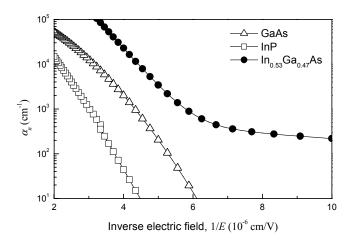

Materials such as In<sub>0.53</sub>Ga<sub>0.47</sub>As, Al<sub>0.48</sub>In<sub>0.52</sub>As, and their alloys, which are lattice-matched to InP (Figure 3.1), are desirable for high-speed and low power applications

Figure 3.1 Bandgap versus lattice constant for various III-V semiconductors. The shaded region contains materials lattice-matched to InP.

due to, for example, the high electron saturation velocity  $(v_{sat,InGaAs} \approx 1 \times 10^7 \text{ cm/sec})$ , high mobility  $(\mu_{n,InGaAs} \approx 15,000 \text{ cm}^2/\text{Vsec})$ , and low bandgap  $(E_{g,InGaAs} \approx 0.77 \text{ eV})^3$  of  $In_{0.53}Ga_{0.47}As$ , and the ability to produce heterostructures with  $Al_{0.48}In_{0.52}As$  ( $\Delta E_c = 0.50 \text{ eV}$ ,  $\Delta E_v = 0.22 \text{ eV}$ ). The applications of such materials have been varied and numerous, 5-14 but the antimony-based materials lattice-matched to InP (i.e.,  $GaAs_{0.49}Sb_{0.51}$ ,  $AlAs_{0.56}Sb_{0.44}$ , and their

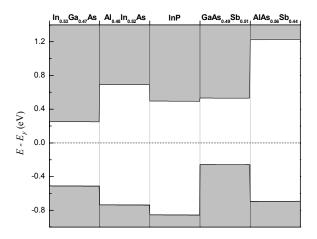

Figure 3.2 Band diagram showing the relative bandgaps and band line-ups for InGaAs, AlInAs, GaAsSb, AlAsSb, and InP.

alloys) have been overlooked until recently as candidates for use in electronic and opto-electronic devices. The benefits of the antimony-based materials, such as larger band offsets ( $\Delta E_c \approx 0.62 \text{ eV}$ ,  $\Delta E_v \approx 0.46 \text{ eV}$ ), <sup>15-17</sup> larger bandgap material ( $E_{g,AlAsSb} \approx 1.92 \text{ eV}$ ), <sup>18</sup> larger index of refraction difference ( $\Delta n_r \approx 0.5$ ), <sup>19</sup> and a material that readily oxidizes (AlAs<sub>0.56</sub>Sb<sub>0.44</sub>), <sup>20-22</sup> have only of late been seen in electronic and opto-electronic applications. <sup>22-32</sup> Table 3.1 shows some material parameters of In<sub>0.53</sub>Ga<sub>0.47</sub>As, Al<sub>0.48</sub>In<sub>0.52</sub>As, GaAs<sub>0.49</sub>Sb<sub>0.51</sub>, AlAs<sub>0.56</sub>Sb<sub>0.44</sub>, and InP.

|                                                                                     | InP       | In <sub>0.53</sub> Ga <sub>0.47</sub> As | $Al_{0.48}In_{0.52}As$       | GaAs <sub>0.49</sub> Sb <sub>0.51</sub> | $AlAs_{0.56}Sb_{0.44}$ |

|-------------------------------------------------------------------------------------|-----------|------------------------------------------|------------------------------|-----------------------------------------|------------------------|

| $\begin{array}{c} \text{Bandgap} \\ \text{Energy,} \\ E_g  (\text{eV}) \end{array}$ | 1.34 (3)  | 0.77 (3)                                 | 1.5 (3)                      | 0.72 (17)                               | 1.92 (18)              |

| $\Delta E_c$ relative to InP (meV)                                                  | -         | -250 <sup>(4)</sup>                      | 250 (4)                      | 120 - 180 (16,17)                       | 740 (33)               |

| $\Delta E_{\nu}$ relative to InP (meV)                                              | -         | 350 <sup>(4)</sup>                       | 130 (4)                      | 620 - 810 (16,17)                       | 160 (15)               |

| $\mu_n$ (cm <sup>2</sup> /Vsec)                                                     | 4000 (34) | ~15,000 (2)                              | ~ 4,000 <sup>(1)</sup>       |                                         | ~ 50                   |

| $\mu_p  (\text{cm}^2/\text{Vsec})$                                                  | 100 (34)  | $\leq 300^{(2)}$                         |                              | ~ 35                                    |                        |

| v <sub>sat</sub> (cm/sec)                                                           |           | $1 \times 10^{7}$ (1)                    | $2.5 - 4 \times 10^{6  (1)}$ |                                         |                        |

Table 3.1 Material properties of InP, InGaAs, AlInAs, GaAsSb, and AlAsSb.

## 3.2 Transistor Design: High Frequency Issues

Given that the goal of this dissertation is the fabrication of a high-speed heterojunction bipolar transistor (HBT) and validation of the oxide aperture HBT design, it is important to understand how material structure and device layout can affect the frequency performance of a device. For HBTs, there are two figures-of-merit that relate various device aspects, which are dependent upon material selection and device layout, to the frequency performance of the transistor: the current-gain cutoff frequency,  $f_{\tau}$ , and the maximum frequency of oscillation,  $f_{max}$ .

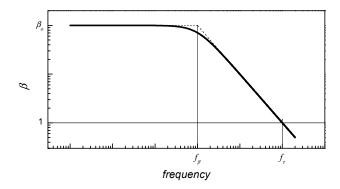

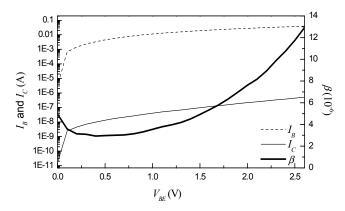

Figure 3.3 gives a classical example of a transistor's common-emitter current gain  $(\beta)$  as a function of operating frequency.  $f_{\tau}$  is defined as the frequency at which  $\beta$  drops to unity, Equation (3.1).

Figure 3.3 Bode plot of common-emitter current gain  $(\beta)$  versus frequency.  $f_{\tau}$  indicates the frequency at which  $\beta = 1$ .  $f_{\beta} = f_{\tau}/\beta_0$  indicates the 3 dB "rolloff" frequency.

$$f_{\tau} = \frac{1}{2\pi} (\tau_E + \tau_B + \tau_C + \tau_{CC})^{-1}$$

(3.1)

$$\tau_{E} = \frac{\eta kT}{qI_{E}} \left( C_{BE} + C_{BC} \right) \simeq \frac{\eta V_{T}}{I_{C}} \left( C_{BE} + C_{BC} \right)$$

$$\tau_{B} = \frac{W_{B}^{2}}{2D_{n}}$$

$$\tau_{C} = \frac{W_{C}}{2v_{sat}}$$

$$\tau_{CC} \simeq \left( R_{E} + R_{C} \right) C_{BC}$$

$$(3.2)$$

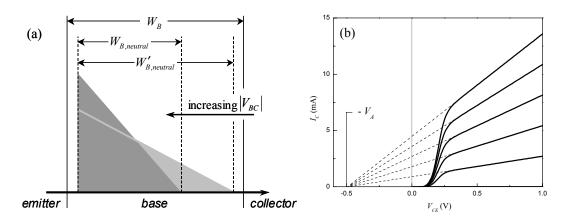

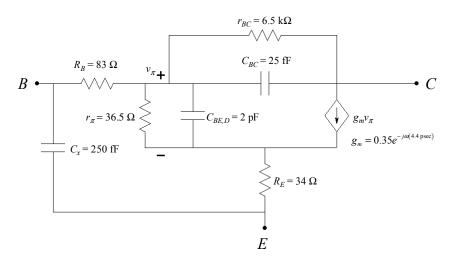

$\tau_E$  is the emitter-charging time associated with charging the base-emitter junction capacitance ( $C_{BE}$ ) and the base-collector junction capacitance ( $C_{BC}$ ) through the base-emitter junction's dynamic resistance ( $r_E = \eta V_T/I_E$ );  $\tau_B$  is the base transit time;  $\tau_C$  is the collector transit time; and  $\tau_{CC}$  is the collector-charging time associated with charging the  $C_{BC}$  through the transistor's emitter and collector resistances,  $R_E$  and  $R_C$  respectively.  $V_T = kT/q$  is the thermal voltage, where k is Boltzmann's constant (8.62 × 10<sup>-5</sup> eV/K), T is the absolute temperature of the semiconductor in Kelvin, and

q is the electronic charge (1.602 × 10<sup>-19</sup> C);  $I_E$  and  $I_C$  are the emitter and collector currents, respectively;  $W_B$  is the width of the neutral base layer;  $D_n$  is the electron diffusion constant in the neutral base;  $W_C$  is the width of the depleted collector; and  $v_{sat}$  is the saturation velocity of electrons in the depleted collector.

A more straightforward understanding of  $f_{\tau}$  may be achieved by examining the roles of the various time constants. As stated previously,  $\tau_E$  and  $\tau_{CC}$  are RC charging times associated with the base-emitter and base-collector junctions. These charging times represent the time that the junctions require to adjust the potential in the base, under given bias conditions (e.g.,  $I_C$ ,  $V_{CE}$ ), in response to a variation in the input current.  $\tau_B$  and  $\tau_C$  are carrier transit times through the neutral base and depleted collector, respectively. Together, ( $\tau_B + \tau_C$ ) represents the time it takes for a charge carrier, once ejected from the emitter, to be imaged or "collected" at the collector contact. Therefore,  $f_{\tau}$  may be thought of representing the total time that the transistor requires to respond to a variation in its input and collect the resultant transited carrier. Figure 3.4 illustrates the various aspects of a HBT and their relations to  $f_{\tau_0}$  as presented in Equations (3.1)-(3.2).

A transistor is said to be "unilateral" when no feedback path exists from the output and to the input of the device. In practice, some amount of feedback always exists, but this can commonly be removed through the use of a lossless feedback network that cancels the innate feedback of the device. The unilateral power gain is the maximum power gain achievable by the transistor.  $f_{max}$  is defined as the

Figure 3.4 Illustration of the various transistor aspects which influence  $f_{\mathbf{r}}$

frequency at which the transistor's unilateral power gain drops to unity, in addition to delineating the boundary between the transistor behaving as an active or passive network, Equation (3.3).

$$f_{max} = \sqrt{\frac{f_{\tau}}{8\pi R_B C_{BC}}} \tag{3.3}$$

$R_B$  is the transistor's base resistance.

The intent of the oxide aperture HBT design is to introduce a method to increase  $f_{max}$  that can be adopted into nearly any material system and existing transistor design. Though it is not of direct concern within the scope of this dissertation, it should be mentioned that there are various means to increase  $f_{\tau}$ . Most of these approaches are dependent upon device layer design and material selection, such as bandgap grading in the base, <sup>7,35</sup> base doping profiles, <sup>36,37</sup> and Schottky collectors; <sup>38</sup> all of which may be adopted into the oxide aperture HBT design.

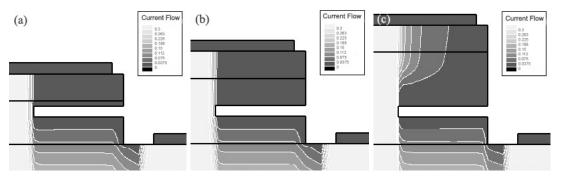

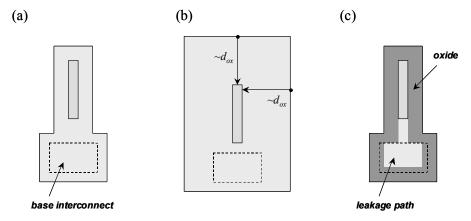

In order to increase the  $f_{max}$  of the transistor, a collector-up design, as opposed to the conventional emitter-up design (Figure 3.5a), was adopted. Using a collector-up

design makes possible the reduction of the transistor's relatively large  $C_{BC}$  by physically reducing the active base-collector junction area, thereby increasing the device's  $f_{max}$ . Simply adopting a plain collector-up design would result in a reduced current gain, or possibly no gain at all, due to an active emitter-base junction that is larger than the corresponding base-collector junction, giving rise to an increased recombination of carriers into the base contacts (Figure 3.5b). Therefore, in order to maintain a high current gain, a current aperture must be introduced into the emitter to channel the carriers that are injected into the base (Figure 3.5c). An additional benefit of the collector-up design is that it easily facilitates the use of a Schottky collector, as

Figure 3.5 (a) Emitter-up design: high gain, high  $C_{BC}$ . (b) Collector-up design: reduced gain, reduced  $C_{BC}$ . (c) Oxide aperture, collector-up design: high gain, reduced  $C_{BC}$ . The arrows represent injected carriers. The dashed perimeter outlines the intrinsic HBT, where transistor action occurs.

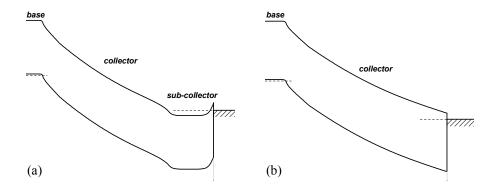

opposed to a conventional ohmic collector/sub-collector commonly used in emitterup designs (Figure 3.6). The benefit of using a Schottky contact for the collector contact is that it removes the collector resistance ( $R_C$ ) from Equation (3.2), reducing the collector-charging time ( $\tau_{CC}$ ), increasing both  $f_{\tau}$  and  $f_{max}$ .<sup>38</sup>

Figure 3.6 (a) Ohmic collector. The sub-collector, though highly conductive, contributes largely to the collector resistance,  $R_C$ . (b) Schottky collector.

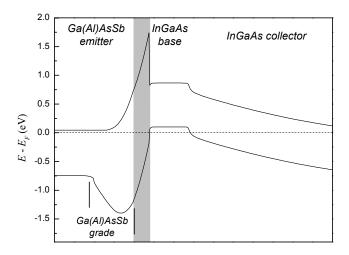

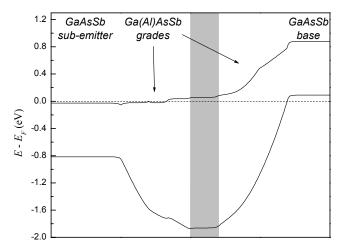

#### 3.3 Transistor Design: Material Selection

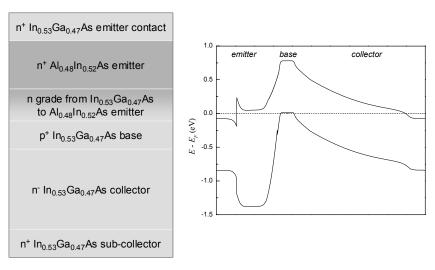

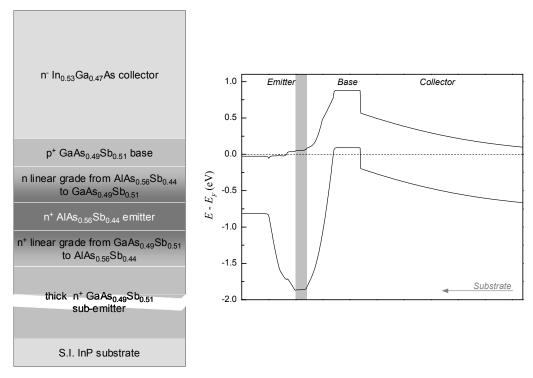

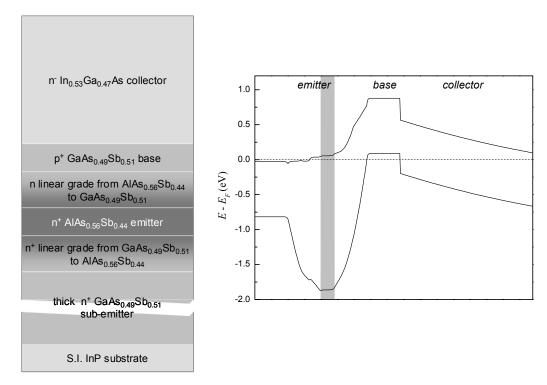

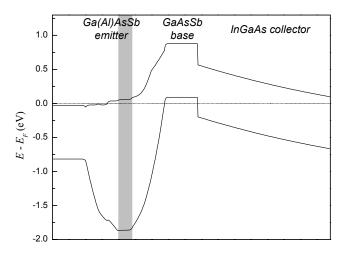

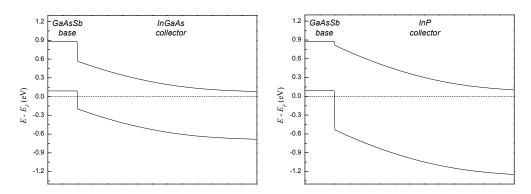

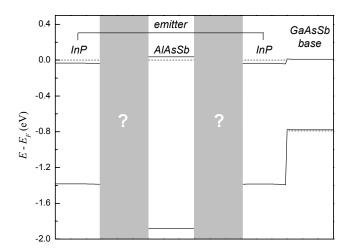

The majority of high-speed HBTs produced today have been InP-based emitter-up HBTs. $^{6,7,39-42}$  A layer structure and band diagram representative of most  $Al_{0.48}In_{0.52}As/In_{0.53}Ga_{0.47}As$  HBTs is presented in Figure 3.7. Alternative designs incorporate an InP emitter, an InP emitter and collector, or an InP emitter and collector with a  $GaAs_{0.49}Sb_{0.51}$  base. $^{25,43,44}$

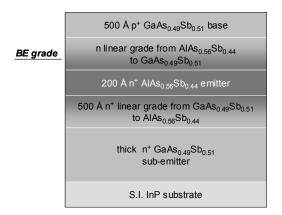

Simply adopting a material structure similar to that in Figure 3.7 for use in the oxide aperture design is not feasible for one reason:  $Al_{0.48}In_{0.52}As$  does not readily oxidize ( $R_{oxidation} \approx 2.4 \,\mu\text{m/hr}$  at 520 °C),  $^{45,46}$  and consequently cannot be used to form a current aperture in the emitter. Therefore, another wide bandgap semiconductor that meets this requirement must be selected. With the advent of the valved antimony source for molecular beam epitaxy (MBE), the growth of mixed group-V compounds, such as  $GaAs_{0.49}Sb_{0.51}$ ,  $AlAs_{0.56}Sb_{0.44}$ , and their alloys, is possible without much difficulty. Therefore, the  $Al_{0.48}In_{0.52}As$  emitter may be replaced with an

AlAs<sub>0.56</sub>Sb<sub>0.44</sub> emitter, which readily oxidizes, in addition to having a somewhat wider bandgap ( $\Delta E_g \approx 0.4 \text{ eV}$ ). Since the band line-up between AlAs<sub>0.56</sub>Sb<sub>0.44</sub> and

Figure 3.7 Layer structure and band diagram of an emitter-up InP-based HBT.

$In_{0.53}Ga_{0.47}As$  is not favorable to the fabrication of an abrupt heterojunction Npn HBT ( $\Delta E_c \approx 0.99 \text{ eV}$ ,  $\Delta E_v \approx 0.19 \text{ eV}$ ) and compositional grading between the two materials is difficult given the disparate group-V elements,  $GaAs_{0.49}Sb_{0.51}$  was selected to replace  $In_{0.53}Ga_{0.47}As$  as the narrow bandgap material in the emitter and base so as to easily facilitate compositional grading and growth of a graded heterojunction HBT. An  $In_{0.53}Ga_{0.47}As$  collector is retained due to its high  $v_{sat}$  and the high selectivity of some wet etches between  $In_{0.53}Ga_{0.47}As$  and  $GaAs_{0.49}Sb_{0.51}$ , simplifying the fabrication of devices.<sup>48</sup>

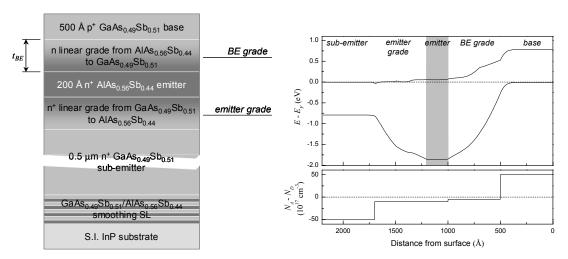

A layer structure of the resultant HBT, accompanied by its band diagram, is shown in Figure 3.8. Detailed layer structures and band diagrams of actual fabricated devices are presented in Chapters 4 and 5.

Figure 3.8 Layer structure and band diagram of the oxide aperture HBT. The shaded region indicates the location of the oxide aperture.

#### 3.4 Growth of $GaAs_{0.49}Sb_{0.51}$ and $AIAs_{0.56}Sb_{0.44}$

"MBE is basically sophisticated thermal evaporation."

—James G. Champlain

The reality is not quite that simple, but essentially the statement is to some extent correct. MBE *is* the condensation of a vapor into a solid, but while it is desirable to form the crystalline solid phase of the semiconductor in question, care must be taken to avoid the formation of other undesirable condensed phases. In order to do so requires that the growth be performed within a series of thermodynamic constraints. These thermodynamic boundaries are commonly referred to as the "MBE growth window". A commonly accepted definition is that, "MBE will thermodynamically be

preferred if it occurs at an overall system composition, temperature, and pressure for which the equilibrium mix of phases is [the crystalline solid and vapor]... "49 Though this is generally a good rule of thumb, it should be noted that there are exceptions; such as the MBE growth of GaN, where the preferred growth conditions are those for a mixture of the crystalline solid phase and Ga-rich liquid, otherwise known as metal-rich or Ga-rich growth; or the MBE growth of low-temperature (LT) grown GaAs, which results in the desirable formation of arsenic precipitates within the GaAs crystal solid due to growth under excessive arsenic flux at low growth temperatures. 51

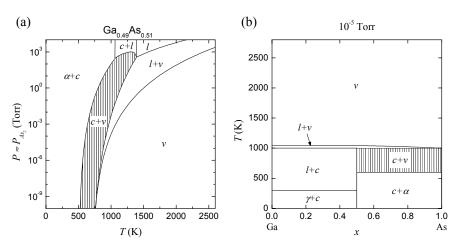

Figure 3.9 shows examples of growth windows for GaAs, a well-established III-V compound semiconductor, presented in terms of phase diagrams. As can be seen

Figure 3.9 After Tsao.<sup>49</sup> (a) P-T phase diagram of  $Ga_{1-x}As_x$  for an overall system composition of x = 0.51. (b) x-T phase diagram for  $Ga_{1-x}As_x$  at a pressure of  $10^{-5}$  Torr. The shaded regions are the preferred MBE growth windows.

from the diagrams, even for the growth of a "simple" binary compound such as GaAs, the grower must monitor and maintain various aspects of the growth environment (e.g., system temperature, pressure, composition) within a specific window. As one

might deduce, as additional elements are added to the crystal; as in classical ternary compounds like  $Al_xGa_{1-x}As$  and  $In_xGa_{1-x}As$ , and the mixed group-V compounds like  $GaAs_{0.49}Sb_{0.51}$  and  $AlAs_{0.56}Sb_{0.44}$ ; the growth window becomes much more restrictive. <sup>49,52-56</sup>

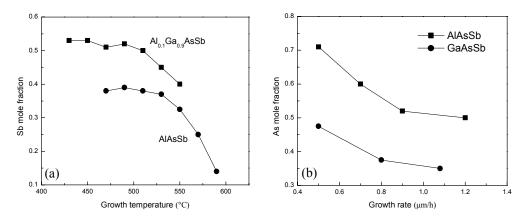

The growth of the mixed group-V compounds GaAs<sub>0.49</sub>Sb<sub>0.51</sub> and AlAs<sub>0.56</sub>Sb<sub>0.44</sub> is further complicated by the non-unity sticking coefficients of antimony and arsenic and by the pronounced temperature dependent exchange of antimony and arsenic atoms on the growth surface. This results in the composition of the arsenide-antimonide compound being not only dependent on the relative arsenic and antimony fluxes, but also on growth temperature, total group-V flux, and growth rate.<sup>27,57</sup> Figure 3.10 shows additional examples of how the composition of various arsenide-antimonide compounds lattice-matched to InP vary with growth temperature and growth rate.

Figure 3.10 After Harmand *et al.*.<sup>27</sup> (a) Antimony mole fraction in AlAsSb and Al<sub>0.1</sub>Ga<sub>0.9</sub>AsSb versus growth temperature. (b) Influence of the growth rate of GaAsSb and AlAsSb on their arsenic mole fraction. Arsenic and antimony fluxes were fixed for each experiment.

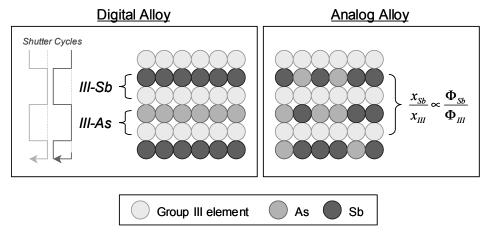

To overcome the difficulties encountered during the growth of arsenide-antimonide compounds, two growth methods have been developed for the growth of GaAs<sub>0.49</sub>Sb<sub>0.51</sub> and AlAs<sub>0.56</sub>Sb<sub>0.44</sub> lattice-matched to InP.<sup>48</sup> The first of the two methods involves the growth of the arsenide-antimonide compound in the form of a digital alloy consisting of the two constituent binary compounds (GaAs/GaSb for GaAs<sub>0.49</sub>Sb<sub>0.51</sub> or AlAs/AlSb for AlAs<sub>0.56</sub>Sb<sub>0.44</sub>) (Figure 3.11). The composition of layers grown by this method has been shown to be highly dependent on group-V shutter duty cycle, while relatively insensitive to any group-V flux variations (especially in the case of arsenic flux variations), resulting in a highly reproducible growth. The major drawback to this method is simply the wear and tear on the MBE

Figure 3.11 Illustration of a digital and an analog arsenideantimonide alloy.

growth system imposed by the numerous shutter operations required. For example, approximately 170 shutter operations per group-V source would be required for just 1000 Å of GaAs<sub>0.49</sub>Sb<sub>0.51</sub> or AlAs<sub>0.56</sub>Sb<sub>0.44</sub>.

The second method requires the correlation of the group-V incorporation rate with its beam equivalent pressure to grow the arsenide-antimonide compound as an analog compound. At growth temperatures below 500 °C the sticking coefficient of antimony approaches unity,<sup>58</sup> this allows for the growth of the arsenide-antimonide compound at its desired composition by simply matching the antimony incorporation rate with the group-III growth rate in the proper ratio (Figure 3.11). For example, if an arsenide-antimonide compound with a desired antimony composition of approximately 50 % (a lattice-matched composition to InP) is grown with a group-III growth rate of 1.0 μm/hr, then the antimony growth rate must be selected to be 0.5 μm/hr. Given that the arsenic sticking coefficient under these conditions is much less than unity, excess arsenic can be supplied to provide an excess group-V background. The group-V incorporation rates can be obtained in-situ by means of group-V reflection high-energy electron diffraction (RHEED) oscillations, similar to ordinary group-III RHEED oscillations.<sup>48</sup>

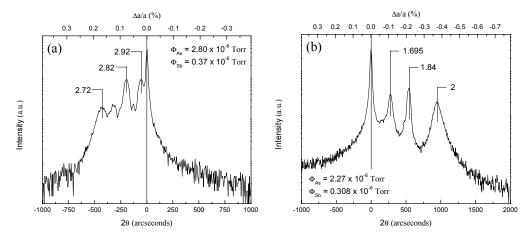

The major drawback to this method of growth is the strong sensitivity of the resultant growth's composition on the relative fluxes of all constituent species. Figure 3.12 shows the variation in lattice mismatch, and hence composition, of  $GaAs_xSb_{1-x}$  and  $AlAsxSb_{1-x}$  ( $x \approx 0.50$ ) on group-III flux. It can be seen that even small deviations in group-III flux (growth rate) results in dramatic effects on composition and the resultant material quality (Figure 3.13).

Though the analog growth of arsenide-antimonide compounds could be considered to be more difficult as compared to the digital growth, once the growth has been calibrated, little upkeep is required to maintain high quality crystal growth, given a stable growth system and periodic calibrations. For this reason, in addition to

Figure 3.12 X-ray diffraction calibrations for (a) GaAsSb and (b) AlAsSb. <sup>59</sup> Both plots are zeroed to the InP substrate x-ray peak. The beam equivalent pressure for both gallium and aluminum fluxes are indicated on the plots in multiples of  $10^{-7}$  Torr.

the greatly reduced wear on the growth system, the analog method of growth was adopted for all growths of GaAs<sub>0.49</sub>Sb<sub>0.51</sub> and AlAs<sub>0.56</sub>Sb<sub>0.44</sub> in this dissertation.

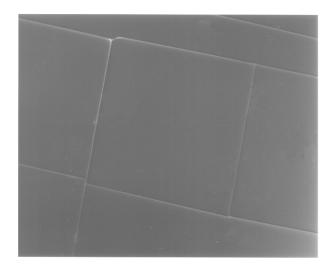

Figure 3.13 Photograph of 0.37 % mismatch growth of AlAsSb.  $^{60}$

### 3.5 Growth of Al<sub>x</sub>Ga<sub>1-x</sub>As<sub>v</sub>Sb<sub>1-v</sub> Lattice-Matched to InP

By selecting a single set of arsenic and antimony fluxes for both  $GaAs_{0.49}Sb_{0.51}$  and  $AlAs_{0.56}Sb_{0.44}$ , the growth of  $Al_xGa_{1-x}As_ySb_{1-y}$  lattice-matched to InP ( $0 \le x \le 1$ ,  $y \approx 0.50$ ) is easily achieved as a simple digital alloy of both ternaries, permitting the trouble-free growth of compositionally graded junctions.

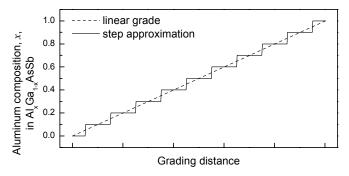

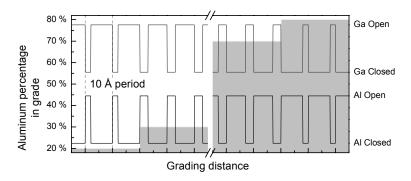

Though growing quarternary alloys and compositional grades by digital methods increases the wear on the system, it is nearly impossible and highly impractical to perform such growths using analog growth techniques. To do so would require calibrations of all constituent fluxes for each composition to be grown and radically increase the difficulty of the growth itself, due to an increased number of group-III cell temperature adjustments and group-V valve adjustments. Therefore, all quarternary alloys in this dissertation have been grown using a digital alloy of both ternaries, GaAs<sub>0.49</sub>Sb<sub>0.51</sub> and AlAs<sub>0.56</sub>Sb<sub>0.44</sub>. Additionally, all grades have been grown using piece-wise step approximations (Figure 3.14 and Figure 3.15).

Figure 3.14 Example of a linear grade of  $Al_xGa_{1-x}AsSb$  from x = 0 to x = 1 using a step approximation. Growth of  $Al_xGa_{1-x}AsSb$  is achieved using a digital alloy of AlAsSb and GaAsSb (Figure 3.15).

Figure 3.15 Detail of the digital composition grade in Figure 3.14. The shutter operations for gallium and aluminum (corresponding to GaAsSb and AlAsSb growth, respectively) are shown in overlay. The period of the digital alloy is 10 Å. Therefore to achieve 20 % Al composition requires the growth of 2 Å of AlAsSb and 8 Å of GaAsSb. 70 % Al composition: 7 Å AlAsSb/3 Å GaAsSb.

#### 3.6 n-type Doping with Tellurium

Silicon is the most widely used element for n-type doping in III-V semiconductors, but as a result of it being a group-IV element, it is also amphoteric by nature. This means that the crystal site (group-III or group-V) that silicon, or any group-IV dopant, occupies determines its doping nature (donor or acceptor). As a consequence of their amphoteric nature, group-IV dopants tend to self-compensate, and at higher concentrations this self-compensation tends to result in a saturation of the carrier concentration.<sup>61</sup>

For most III-V semiconductors, silicon largely occupies the group-III site as a donor, with a small fraction occupying the group-V site as acceptors, resulting in very little compensation and an overall n-type crystal. Conversely, for antimony-based compounds silicon has been shown to generally incorporate as an acceptor,

attributable to the silicon mostly residing on the antimony (group-V) sites, resulting in a p-type crystal. 62,63

For this reason, tellurium, a group-VI element, has been used as an n-type dopant for antimony-based compounds. Because tellurium is not a group-IV element, it does not suffer from self-compensation as silicon does. But like silicon, tellurium suffers from donor-complex (DX) center formation in compounds containing aluminum, which can greatly reduce its doping efficiency. 65

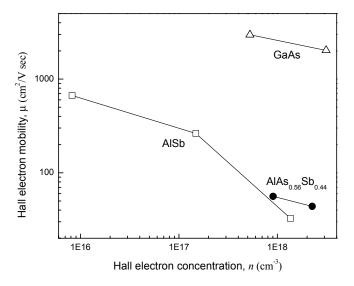

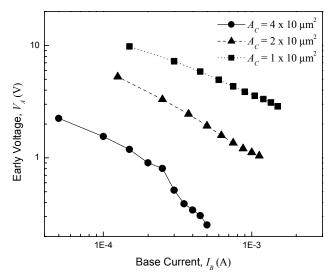

An additional problem encountered with doping the arsenide-antimonides is the poor mobility of carriers at high doping levels, especially in AlAs<sub>0.56</sub>Sb<sub>0.44</sub> (Figure 3.16). This along with the restricted doping level leads to relatively high resistivities, complicating device design.

Figure 3.16 Plot of electron mobility versus electron concentration, measured by Hall effect, for various semiconductors doped with tellurium, Te.

### 3.7 Oxidation of AIAs<sub>0.56</sub>Sb<sub>0.44</sub>

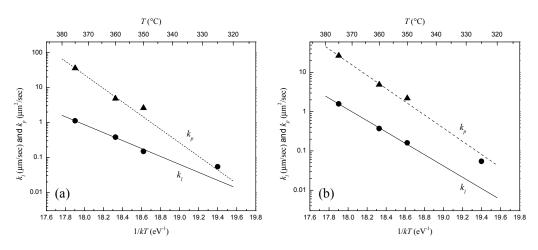

The oxidation of  $AlAs_{0.56}Sb_{0.44}$ , like  $Al_xGa_{1-x}As$ , <sup>66-68</sup> can be described using the Deal-Grove model for oxidation. <sup>69</sup> Equation (3.4) shows the characteristic equation associated with this model.

$$t = \frac{d}{k_l} + \frac{d^2}{k_p} \tag{3.4}$$

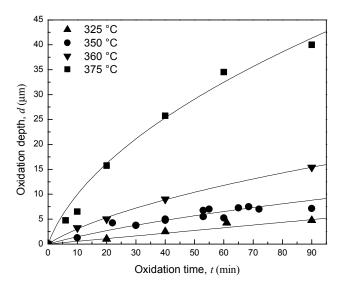

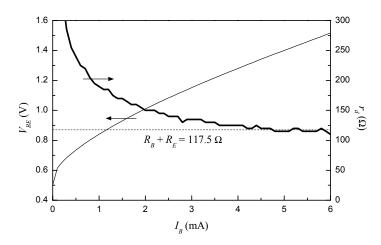

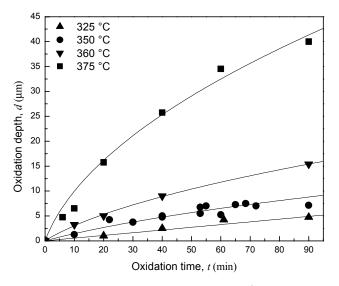

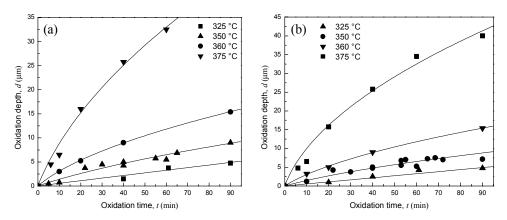

Where t is the oxidation time, d is the oxidation depth,  $k_l$  is the linear oxidation constant, and  $k_p$  is the parabolic oxidation constant. Figure 3.17 shows an exemplar of the oxidations performed in this work and the associated fitted curves using

Figure 3.17 Oxidation depth versus oxidation time for a sample with a 500 Å emitter grade, a 200 Å AlAsSb layer, and a 500 Å base-emitter (BE) grade. Water temperature was 90 °C, nitrogen flow rate was 1.2 lpm, furnace temperature is indicated on the plot.

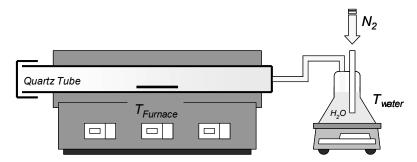

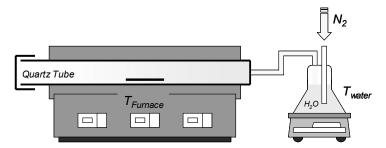

Equation (3.4). The oxidations in this work were performed using a three-zone furnace; into which pre-heated water vapor was carried by nitrogen gas. Unless

otherwise stated, the water temperature and nitrogen flow rate may be assumed to have been 90 °C and 1.2 lpm, respectively. An illustration of the furnace is shown in Figure 3.18.

Though a conclusive study has not been performed, the work in this dissertation suggests that there were no semi-metallic antimony layers formed. It is hypothesized

Figure 3.18 Illustration of the oxidation furnace and water vapor bubbler.

that this is due to the fact that the AlAs<sub>0.56</sub>Sb<sub>0.44</sub> layers oxidized in this work were simply too thin to supply enough antimony to form a continuous layer.

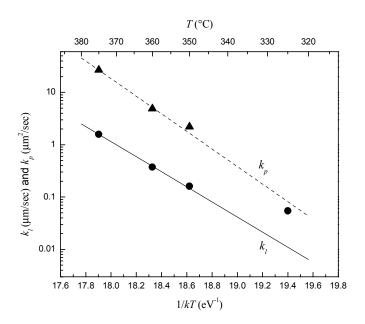

As is the case with  $Al_xGa_{1-x}As$  compounds,  $^{66,68,70-72}$   $AlAs_{0.56}Sb_{0.44}$  exhibits an oxidation characteristic that is dependent upon oxidation temperature. From Figure 3.17 it can be seen that as the oxidation temperature increases, the oxidation rate of  $AlAs_{0.56}Sb_{0.44}$  rapidly increases. This is reflected in how the linear oxidation constant,  $k_l$ , and the parabolic oxidation constant,  $k_p$ , vary with temperature. Figure 3.19 shows a plot of  $k_l$  and  $k_p$  versus 1/kT for the curves presented in Figure 3.17.

From Figure 3.19, as the oxidation temperature increases, both  $k_l$  and  $k_p$  increase with an Arrhenius-like behavior. Though it appears that the oxidation characteristic

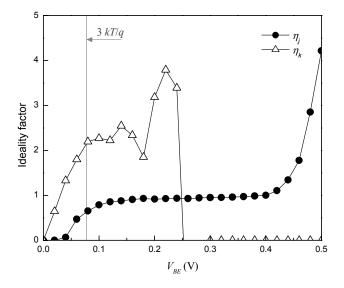

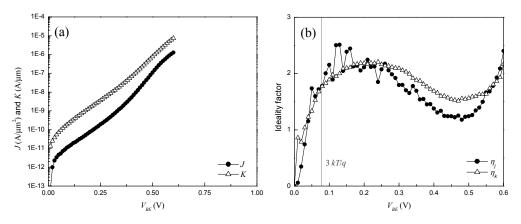

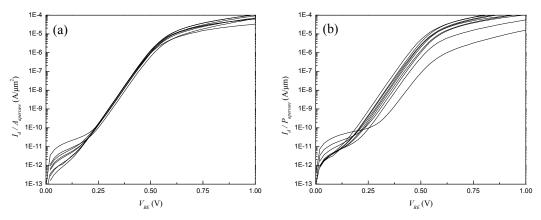

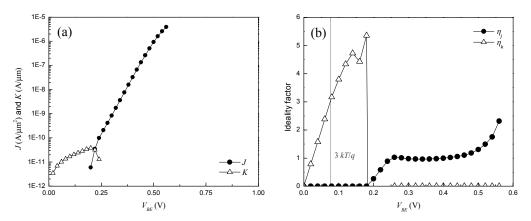

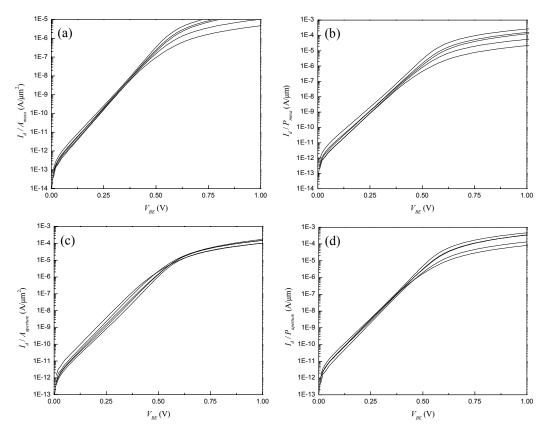

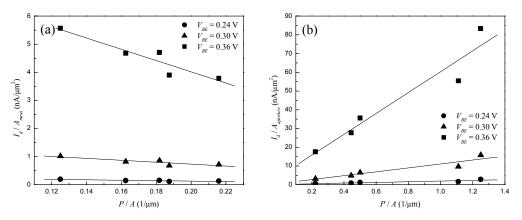

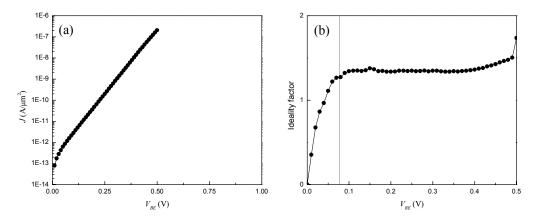

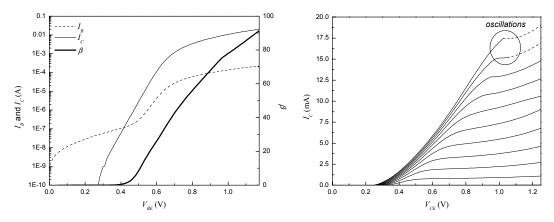

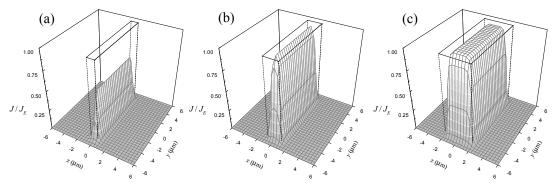

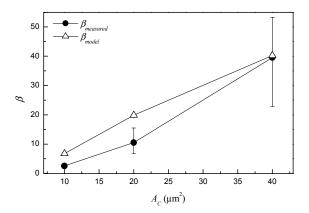

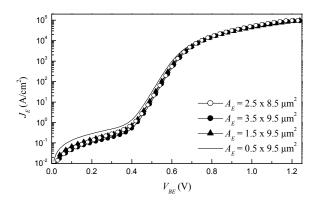

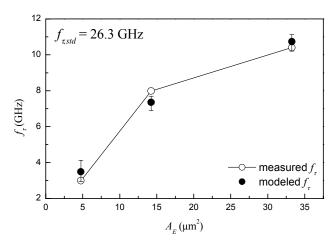

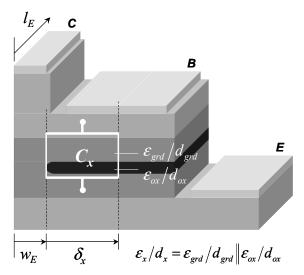

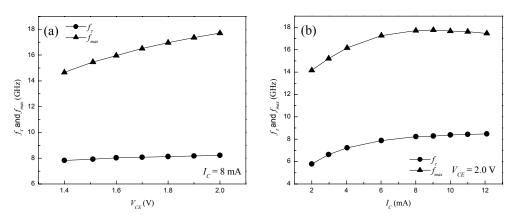

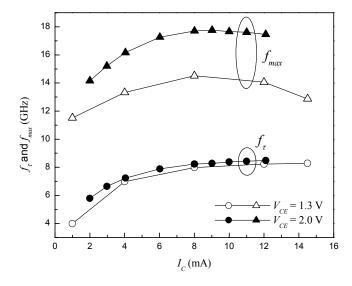

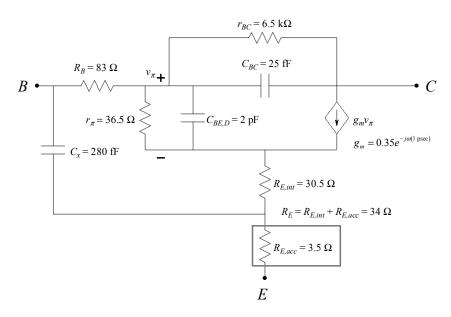

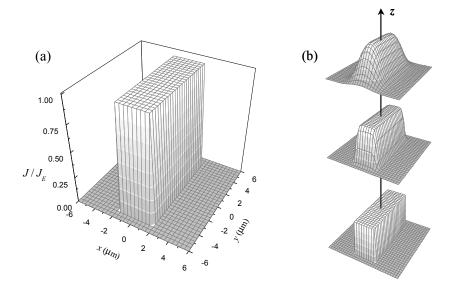

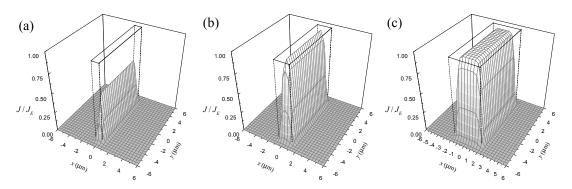

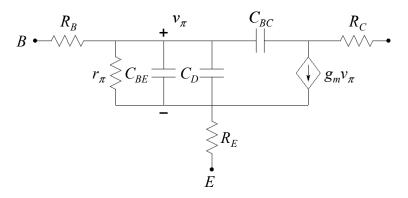

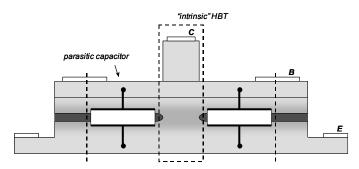

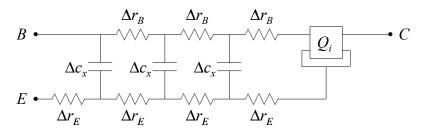

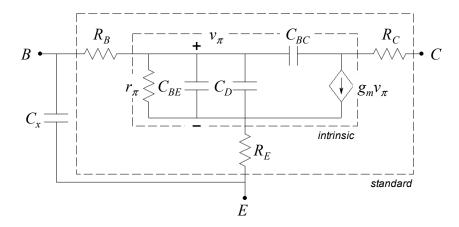

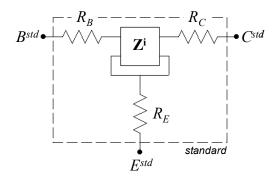

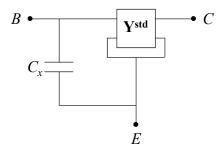

in Figure 3.17 becomes more diffusion limited at higher temperatures, the activation energies of the linear and parabolic rate constants,  $E_{A,k_l}$  and  $E_{A,k_p}$  respectively, are nearly equivalent ( $E_{A,k_l} = 3.32 \text{ eV}$ ,  $E_{A,k_p} = 3.87 \text{ eV}$ ) for the temperature range examined in this dissertation.